# Graphene/MoS<sub>2</sub> Hybrid Technology for Large-Scale Two-**Dimensional Electronics**

Lili Yu,\*\*,† Yi-Hsien Lee,‡ Xi Ling,† Elton J. G. Santos,<sup>§,#</sup> Yong Cheol Shin,<sup>||</sup> Yuxuan Lin,† Madan Dubey,<sup> $\perp$ </sup> Efthimios Kaxiras,<sup>§,¶</sup> Jing Kong,† Han Wang,\*\*,†, $\triangle$  and Tomás Palacios\*\*,†

Supporting Information

ABSTRACT: Two-dimensional (2D) materials have generated great interest in the past few years as a new toolbox for electronics. This family of materials includes, among others, metallic graphene, semiconducting transition metal dichalcogenides (such as MoS<sub>2</sub>), and insulating boron nitride. These materials and their heterostructures offer excellent mechanical flexibility, optical transparency, and favorable transport properties for realizing electronic, sensing, and optical systems on arbitrary surfaces. In this paper, we demonstrate a novel technology for constructing large-scale electronic systems based on graphene/molybdenum disulfide (MoS<sub>2</sub>) heterostructures grown by chemical vapor deposition. We have fabricated highperformance devices and circuits based on this heterostructure, where MoS<sub>2</sub> is used as the transistor channel and graphene as contact electrodes and circuit interconnects. We provide a systematic comparison of the graphene/MoS2 heterojunction contact to more traditional MoS2-metal junctions, as well as a theoretical investigation, using

density functional theory, of the origin of the Schottky barrier height. The tunability of the graphene work function with electrostatic doping significantly improves the ohmic contact to MoS<sub>2</sub>. These high-performance large-scale devices and circuits based on this 2D heterostructure pave the way for practical flexible transparent electronics.

KEYWORDS: Molybdenum disulfide, graphene, heterostructure, field-effect transistor, integrated circuits, flexible and transparent

As Moore's law approaches its physical limit in Si-based electronics, the device research community has been actively searching for new material options that can push performance beyond its traditional boundaries. The emerging alternative, two-dimensional (2D) materials, offers many unique properties, making this class of materials very attractive for extending electronics into new application domains. In particular, 2D materials<sup>1-5</sup> with their excellent mechanical flexibility and transport properties have attracted great interest as a high-mobility alternative to organic semiconductors<sup>6,7</sup> and Si nanoribbons;8 these 2D materials could lead to the realization of transparent and bendable electronic systems that can be placed on a wide variety of surfaces. To harvest their full advantage in bendable electronics, it is highly desirable to construct systems solely based on 2D materials and their heterostructures. 9-11 So far, the circuits that have been constructed based on 2D materials typically rely on a metal to form contacts and interconnects,  $^{12-15}$ which is one of the key limitations on the circuit flexibility. Although there are a few reports using graphene as contacts of 2D material devices, the demonstration often remains at the level of a single device based on the nonscalable exfoliated flakes and there has been no effort reported to tune the contact performance. 10,16 Besides, a high-quality junction between semiconductor and metallic contact with no energy barrier is crucial for high-performance device, which is hard to achieve for 2D transition metal dichalcogenide (TMD) because of their large bandgap. In particular, it is essential to study the critical issues of large-scale heterogeneous integration of 2D materials and performance of graphene/2D-semiconductors. In this Letter, we address two crucial issues on future applications of 2D electronics: (i) We present the first demonstration of integrated graphene/molybdenum disulfide (MoS<sub>2</sub>) heterostructures using a scalable chemical vapor deposition (CVD) process. Specifically,

Received: December 26, 2013 Revised: April 19, 2014 Published: May 8, 2014

Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, 77 Massachusetts Avenue, Cambridge, Massachusetts 02139, United States

<sup>\*</sup>Materials Science and Engineering, National Tsing-Hua University, Hsinchu, 30013, Taiwan

<sup>§</sup>School of Engineering and Applied Sciences, Harvard University, Cambridge, Massachusetts 02138, United States

Department of Materials Science and Engineering, Massachusetts Institute of Technology, 77 Massachusetts Avenue, Cambridge, Massachusetts 02139, United States

<sup>&</sup>lt;sup>1</sup>United States Army Research Laboratory, 2800 Powder Mill Road, Adelphi, Maryland 20783-1197, United States

<sup>&</sup>lt;sup>¶</sup>Department of Physics, Harvard University, Cambridge, Massachusetts 02138, United States

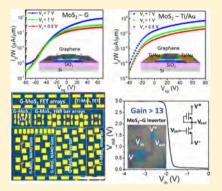

Figure 1. (a) Optical micrograph and AFM data (inset) of a single-layer (SL) chemical vapor deposition (CVD) grown  $MoS_2$  thin film. (b) Raman spectroscopy of as-grown SL CVD  $MoS_2$  thin film (red line) and the CVD graphene/ $MoS_2$  structure. (c) Schematic illustration of important fabrication steps to make large-scale electronics from graphene/ $MoS_2$  heterostructure using  $MoS_2$  as channel and graphene as contact electrodes and interconnects. (d) Optical micrograph (left) and AFM (right) of CVD  $MoS_2$  dual gate transistor with graphene as electrodes. The scale bar in AFM image is 10 μm. (e) Optical micrograph of large-scale chip of  $MoS_2$  devices and circuits using CVD graphene as electrodes and interconnects (white dashed box) as well as control devices and circuits using Ti/Au electrodes in adjacent (red dashed box). Metal pads (gold color) are fabricated on the sample for convenient measurement. The scale bar is  $SOO \mu m$ .

we have fabricated both discrete transistors and fully integrated logic circuits using  $MoS_2$  as the channel and graphene as contacts and interconnects by developing a new technology that allows the selective etching of 2D materials. This process can be used to fabricate any 2D heterojunction in large scale. (ii) We report on the performance of graphene-based contacts in  $MoS_2$  field effect

transistors (FETs) and systematically benchmark them against its metal counterparts. We find that the tunable Fermi level in graphene allows excellent work-function match with  $MoS_2$ , leading to low contact resistance.

Recently, high-quality TMD monolayers, including MoS<sub>2</sub> and WS<sub>2</sub>, have been directly synthesized on diverse surfaces using a

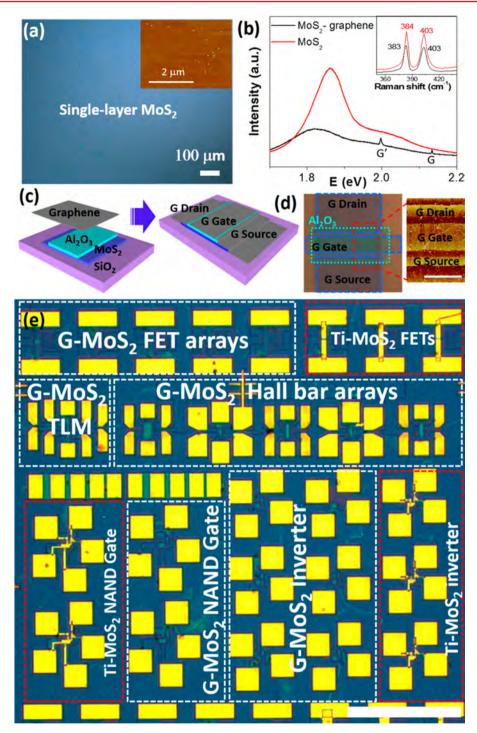

Figure 2. Back-gated transport properties of  $MoS_2$ /graphene  $(MoS_2-G)$  and  $MoS_2$ -Ti FETs performance at room temperature. (a) Output performance of a representative  $MoS_2-G$  transistor at large field and small field with both negative and positive biases (inset). (b) Transfer characteristics of  $MoS_2-G$  transistor with current density on the left axis and transconductance/width on the right axis. (c) Field effect mobilities in  $MoS_2-G$  and  $MoS_2-Ti$  FETs at different source drain voltages. (d) Same as in (b) for the control system  $MoS_2-Ti$ .

scalable CVD process with the seeding of perylene-3,4,9,10tetracarboxylic acid tetrapotassium salt (PTAS). 17,18 Highquality and large-area MoS2 monolayers were obtained using this technique, leading to the demonstration of highly scalable electronics based on this atomically thin material. 15 We have used these MoS<sub>2</sub> monolayers as the channel of transistors. Details of the growth are described in the Supporting Information. An optical image of as-grown CVD MoS2 is shown in Figure 1a, demonstrating a good uniformity and a high coverage approaching 100%. The sample is continuous over a size of 2  $\times$  2 cm<sup>2</sup>, ending with isolated triangular MoS<sub>2</sub> structures at the edge (Figure S1b, Supporting Information). Atomic force microscopy (AFM) is conducted at one of the isolated triangles to get the thickness of MoS<sub>2</sub> (shown in Figure S1c, Supporting Information). The thickness of the CVD MoS<sub>2</sub> monolayer is  $\sim$ 8 Å, which is consistent with the values of MoS2 monolayer reported elsewhere. Raman and photoluminescence (PL) spectroscopy were performed using a 532 nm Nd:YAG laser on the sample to investigate the quality of MoS<sub>2</sub>, see Figure 1b. The single-layer structure of as-gown MoS<sub>2</sub> is confirmed from its Raman spectroscopy based on the peak spacing between the  $E_{2\sigma}$ mode and the  $A_{1g}$  mode, which is smaller than 20 cm<sup>-1</sup> (Figure 1b, inset). A strong photoluminescence peak located at 1.88 eV shown in Figure 1b corresponds to the carrier recombination across the direct bandgap of single-layer  ${\rm MoS_2}^{19,20}$  and implies a high quality of MoS<sub>2</sub> monolayer. Because of the large excitonic binding energy in  $MoS_2$  (0.4–0.8 eV, from theoretic calculation),<sup>21–23</sup> the electronic band gap is estimated to be larger than 2.3 eV, which makes it harder to get good contact with than few layer  $MoS_2$  (bandgap of 1.2 eV). In graphene/ $MoS_2$  heterostructures (Figure 1b, black line), the PL intensity is quenched because the metallic nature of graphene and the PL peak shift to negative value, possibly from doping effect. The two peaks at 2.0 and 2.14 eV come from graphene Raman peak of G' and G. There is negligible change in the peak spacing between the  $E_{2\rm g}$  mode and the  $A_{1\rm g}$  mode in this hybrid structure. <sup>24</sup>

CVĎ-MoS<sub>2</sub> monolayers grown on a 300 nm SiO<sub>2</sub>/Si substrate were first patterned to form transistor channels using electron beam lithography (EBL) with poly(methyl methacrylate) (PMMA) as the resist. After developing the resist pattern, the exposed parts of the MoS<sub>2</sub> sheet are etched away using oxygen plasma to achieve device isolation. The sample was then coated with a methyl methacrylate (MMA) (6% concentration in ethyl lactate)/PMMA (2% concentration in anisole) stack, followed by EBL exposure and development, forming a double-layer structure with openings on MMA slightly wider than on PMMA. Subsequently, 20 nm aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) was deposited by atomic layer deposition (ALD) at 100 °C (below the glass transition temperature of PMMA/MMA stack<sup>25</sup>) using trimethylaluminum (TMA) and water as precursors (see Methods), followed by liftoff to form a patterned Al<sub>2</sub>O<sub>3</sub> etchstop layer. Large-area single layer graphene was then grown on copper foils at 1035 °C by CVD method<sup>26,27</sup> and transferred<sup>28,29</sup> (Supporting Information) onto the sample, see Figure 1c, left panel. Following a new EBL step, patterned areas of graphene were etched by oxygen plasma to define the source, drain, and

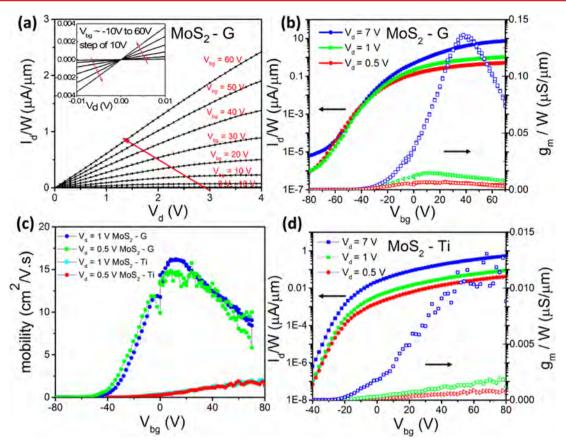

Figure 3. (a) Output characteristics ( $I_d$  vs  $V_d$ ) and (b) transfer characteristics ( $I_d$  vs  $V_{tg}$ ) of top-gated MoS<sub>2</sub> transistor with Al<sub>2</sub>O<sub>3</sub> as top gate dielectric, graphene as source, drain, and gate electrodes.  $V_{tg}$  is the top gate voltage. (c) Output voltage as a function of the input voltage for a MoS<sub>2</sub>–G logic inverter. Optical image (inset at lower left corner) and schematic of the electronic circuit (inset at upper right corner) for the inverter. (d) The gain of the inverter, which is larger than 12.

gate of the transistor, while the  $\mathrm{MoS}_2$  channels were protected by the  $\mathrm{Al}_2\mathrm{O}_3$  etch-stop layer, see Figure 1c, right panel. The sample was then cleaned by acetone and annealed to remove PMMA residues. (Alignment accuracy of this process and alternate lithography methods for EBL is discussed in Supporting Information). By using patterned etch stop with specific design, we are able to make any 2D heterojunction in wafer scale. This pave the way for large-scale application of 2D heterojunction devices, such as heterojunction laser, photodetector, heterojunction bipolar transistors, tunneling FET, high-electronmobility-transistor, etc.

Schematic and optical micrograph images of a dual gate FET are shown in Figure 1c (right panel) and Figure 1d, respectively. This device (MoS<sub>2</sub>-G FET) has MoS<sub>2</sub> as channel, ALD Al<sub>2</sub>O<sub>3</sub> as top gate dielectric, and graphene as source, drain and gate electrodes (connected to metal pads for measurement) and SiO<sub>2</sub>/Si as back gate. In Figure 1d, the single layer graphene and single layer MoS<sub>2</sub> can be clearly distinguished through the optical contrast because of the thin material structure and interference effect between the graphene and MoS<sub>2</sub> with the SiO<sub>2</sub>/Si substrate underneath with orange background for SiO2, bright blue squares for Al<sub>2</sub>O<sub>3</sub>, blue for MoS<sub>2</sub>, and grayish purple for graphene. In the AFM image of the channel region, Figure 1d right panel, the signature wrinkles on the CVD graphene can be clearly seen. The surface of the low-temperature ALD Al<sub>2</sub>O<sub>3</sub> layer is uniform and free of pinholes, with a dielectric thickness of 20 nm as measured by AFM. Using this large-scale hybrid structure process, we have successfully fabricated various devices and integrated circuits on a single chip, shown in Figure 1e. FETs, Hall bars, and transmission line method (TLM) structures were made to

characterize the material properties and device performance, while inverters and NAND gates demonstrate the scalability and the potential of this technology for mass production. On the same chip, a batch of control devices and circuits were also fabricated with 15 nm Ti/45 nm Au metal stacks as electrodes (MoS2-Ti devices and circuits), shown in red dashed-line rectangles in Figure 1e. We chose Ti here because it is the most commonly used metal for MoS<sub>2</sub> FET research<sup>1,30</sup> and has been proposed as excellent metal contacts for n-type MoS<sub>2</sub> FET in previous theoretical papers.<sup>31,32</sup> The MoS<sub>2</sub>—Ti devices and circuits were also fabricated with Al<sub>2</sub>O<sub>3</sub> as top dielectric layers and graphene as top gate in order to eliminate the effect from high- $\kappa$  dielectric and top/back gate couplings while investigating the role of the source drain contacts. This is the first time largescale graphene/MoS<sub>2</sub> hybrid 2D electronics, both grown using CVD methods in their single-layer form, were fabricated using a CMOS-compatible, fully integrated process.

All the fabricated devices and circuits were measured in a vacuum probe station (Lakeshore cryogenics) at a pressure of  $\sim$ 3  $\times$  10<sup>-6</sup> Torr. During the back-gate sweep measurements, the top gates are grounded to avoid the coupling between top and back gates.<sup>33</sup> We studied about 50 devices that showed highly reproducible performance. Representative back-gated transport characteristics of the MoS<sub>2</sub>–G transistor are shown in Figure 2a,c with a device channel length of 12  $\mu$ m and width of 20  $\mu$ m. Figure 2a shows the output performance ( $I_{\rm ds}$  vs  $V_{\rm ds}$ ) of the devices. The current is linear with small source-drain biases (10 meV), indicating that the contact between graphene and MoS<sub>2</sub> is ohmic. The symmetry of the current with respect to the origin at positive and negative biases (inset of Figure 2a) further verifies the ohmic

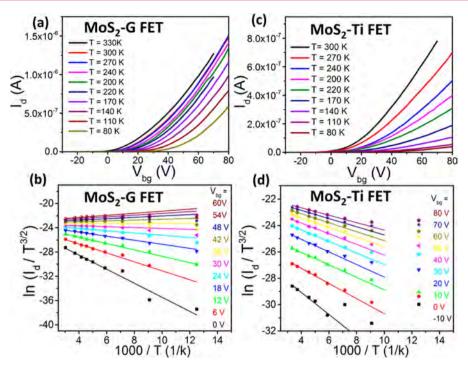

**Figure 4.** Temperature-dependent transport, that is,  $I_d - V_{bg}$  curves at various temperatures: (a,b) MoS<sub>2</sub>–G FET, (c,d) MoS<sub>2</sub>–Ti FET. The source drain bias for both structures are 0.5 V during measurement. In (b,d) we show the linear fit of Arrhenius plot  $\ln(I_d/T^{3/2})$ ) vs 1000/T.

nature of the contacts. The transfer characteristics ( $I_{\rm ds}$  vs  $V_{\rm bg}$ ) of MoS2-G and MoS2-Ti FETs (used as control devices with exactly the same geometry) are shown in log scale in Figure 2b,d, respectively. They both have on/off ratios larger than 10<sup>6</sup>. The current density is 8  $\mu$ A/ $\mu$ m at  $V_d$  = 7 V,  $V_{bg}$  = 60 V for MoS<sub>2</sub>-G FET, about 12 times higher than that of MoS<sub>2</sub>-Ti, because of the lower barrier between MoS2 and graphene than that between  $MoS_2$  and Ti. The transconductance per channel width  $(g_m/W =$  $dI_d/dV_{bg}/W$ ) of MoS<sub>2</sub>-G is 0.15  $\mu$ S/ $\mu$ m with 300 nm SiO<sub>2</sub> back gate oxide, more than 1 order of magnitude higher than that of MoS<sub>2</sub>-Ti structures. The field effect mobilities calculated from the transfer characteristics are shown in Figure 2c. The field effect mobility is calculated using expression  $\mu = [dI_d/dV_{bg}] \times [L/V_{bg}]$  $(WC_{ox}V_{d})$ ], where  $V_{bg}$  and  $V_{d}$  are the back-gate voltage and source-drain voltage, L and W are the channel length and width, and  $C_{ox}$  (11 nF) is the capacitance per unit area between the channel and the back gate (calculated from 300 nm SiO<sub>2</sub>). The mobility of MoS<sub>2</sub> in MoS<sub>2</sub>-G structures reaches the peak value of  $17 \text{ cm}^2/(\text{V s})$ , while the MoS<sub>2</sub>-Ti structure has a peak mobility of only about 1.8 cm<sup>2</sup>/(V s). This value could be further improved by elimination of trapping states and by using substrates such as boron nitride (BN) to reduce surface roughness and block substrate charge. 34 The measured I-Vcharacteristics are fitted to a classic drift-diffusion model to extract the contact resistance for MoS<sub>2</sub>-G and MoS<sub>2</sub>-Ti FETs. The effective gate voltage  $V_{\rm gs\_eff}$  and source drain voltage  $V_{\rm ds\_eff}$  are given by  $V_{\rm gs-eff} = V_{\rm gs} - R_{\rm s}I_{\rm ds}$ ,  $V_{\rm ds-eff} = V_{\rm ds} - (R_{\rm s} + R_{\rm d})I_{\rm ds}$ , with  $R_{\rm s}$ ,  $R_{\rm d}$  the parasitic series source/drain contact resistances. The contact resistance is 0.1 and 1 k $\Omega$  mm for MoS<sub>2</sub>-G and MoS<sub>2</sub>-Ti, respectively. The single layer MoS<sub>2</sub> has larger bandgap than multilayer MoS<sub>2</sub> and the CVD sample has lower doping concentration than flakes exfoliated from the mineral. These result in lower density of state, making it more difficult to achieve good contacts to single layer CVD MoS<sub>2</sub> compared to multilayer flakes, as was also found in other literature reports. 3,35 More work is needed to further decrease the contact resistance, especially by

degenerate doping of the  $MoS_2$  layer. The  $MoS_2$ –G contact in the present work exhibits a state-of-the-art contact resistance between CVD  $MoS_2$  and CVD graphene. The use of graphene as contacts for  $MoS_2$  FETs, as discussed above, provides 10 times lower contact resistance and 10 times higher on-current and field-effect mobility than conventional  $MoS_2$ -metal contacts. In addition, it has been shown in previous work that graphene- $MoS_2$  junction is robust with strain of 1.5%. This new contact scheme is expected to also benefit flexible electronics, where most device failures are typically related to crack formation in the metal electrodes. In addition, graphene can act as transparent electrode for  $MoS_2$  optical devices, because the sputtering process commonly used in the deposition of transparent metal indium tin oxide (ITO) is not compatible with fragile single-layer  $MoS_2$ .

The top-gated performance of the MoS<sub>2</sub>-G transistors is plotted in Figure 3. The output characteristics show a linear current behavior at low drain bias voltages (0.5 eV), and current saturation at higher biases. In the linear regime at small sourcedrain voltages, the current is proportional to  $V_{ds}$ , indicating that the source and drain electrodes made of graphene form ohmic contact with MoS<sub>2</sub>. The current saturates at higher drain bias ( $V_{\rm ds}$ >  $V_{\rm tg}$  –  $V_{\rm tr}$  where the  $V_{\rm tg}$  is the top-gate voltage while  $V_{\rm t}$  is the threshold voltage of the device) due to the formation of depletion region on the drain side of the gate, as is typical of long channel MOSFETs. The onset for current saturation because of channel pinch-off follows the relationship  $V_{\rm ds}$  >  $V_{\rm tg}$  —  $V_{\rm t}$  with  $V_{\rm t}$  = -1.7 V. The transfer characteristics are shown in Figure 3b. The results show the on-off ratio of the device is larger than 10<sup>3</sup>. The transconductance in this device is 0.5  $\mu$ S/ $\mu$ m at  $V_{\rm d}$  = 7 V (Figure S3a, Supporting Information). The transconductance drops at the high gate voltage region, because of the access resistance. Further development of self-aligned technology or doping of the access regions could help solve this problem. The subthreshold swing is 150 mV (Figure S3b, Supporting Information), corresponding to a midgap interface trap density value of 2.7 ×

$10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup>, using the value of  $C_{\rm ox}$  calculated from 20 nm thick Al<sub>2</sub>O<sub>3</sub> with a dielectric constant of 7.

Using the technology described above, we have built several basic integrated logic circuits. For example, a fully integrated inverter was fabricated in depletion mode transistor resistor configuration, using two  $\rm MoS_2-G$  FETs, shown in Figure 3c. The two transistors act as a switching and a load resistor, respectively (see schematic diagram, Figure 3c inset). The output characteristics of the inverter are shown in Figure 3c. A low voltage of -4 V represents a logic state 0 and a voltage close to 0 V represents logic state 1. The inverter is able to be operated under a supply voltage ( $V_{\rm dd}$ ) of 3 V, as shown in Figure 3c. The voltage gain is close to 12, as shown in Figure 3d. This is the first demonstration of logic circuits using CVD-grown 2D heterostructures that is mass producible. Further improvement in device and circuit performance can be achieved by changing the dielectric layers to insulating 2D crystals such as hexagonal boron nitride or 2D oxides.  $^{9-11,37-39}$

The results from our FETs and circuits demonstrate the advantages of graphene as a contact material for 2D electronic systems. They also highlight the key role of the interfacial barrier height between the active channel and electrodes in device performance. In the following, we give a systematic comparison of the barrier between  $MoS_2$ /graphene and that between  $MoS_2$ —Ti in the control structure. To study the barrier height we have characterized the transport properties at different temperatures and fitted the data using a thermionic emission model (Figure 4). The current through a Schottky barrier into 2D material can be described using the 2D thermal emission equation

$$\begin{split} I_{\rm d} &= A T^{3/2} {\rm exp} \bigg( \frac{-q \varphi_{\rm B}}{k_{\rm B} T} \bigg) \bigg[ {\rm exp} \bigg( \frac{q V_{\rm d}}{n k_{\rm B} T} \bigg) - 1 \bigg] \\ &= I_{\rm s} \bigg[ {\rm exp} \bigg( \frac{q V_{\rm d}}{n k_{\rm B} T} \bigg) - 1 \bigg] \end{split}$$

where  $I_d$  is the current, A is Richardson's constant, T is the temperature,  $\phi_{\mathrm{B}}$  is the barrier between the metal and semiconductor,  $k_{\rm B}$  is the Boltzmann constant, q is the electronic charge,  $V_d$  is the source to drain bias, and n is the nonideal factor of the Schottky diode. The power law of  $T^{3/2}$  comes from the Boltzmann carrier distribution and the thermal velocity. It is less than  $T^2$  commonly found in a 3D system because of the constant value of the density-of-states in a 2D system. 40 n is calculated by fitting the  $I_d$  versus  $V_d$  curves using the expression  $I_d$  =  $I_s[\exp(q(V_d - I_d R_s)/nk_B T) - 1]$ , where  $R_s$  is the series resistance from the device channel (see details in Supporting Information). The current as a function of back gate bias for the MoS<sub>2</sub>-G FET at different temperatures is shown in Figure 4a and that for the MoS<sub>2</sub>-Ti FET in Figure 4c. For both structures, the current decreases as temperature decreases. However, the temperature dependence in  $MoS_2$ -G is much weaker than that of  $MoS_2$ -Ti, indicating a smaller thermal emission barrier in the MoS2-G structure. In MoS2-G, the threshold voltage shifts to more positive values with decreasing temperature (Figure S4, Supporting Information) and the mobility remains almost constant with the same gate overdrive  $V_{

m bg}-V_{

m t}$ . In the MoS $_2-$ Ti structure, the threshold voltage does not change, while the transconductance or mobility decreases with decreasing temperature (see Figure S5, Supporting Information). To determine the Schottky barrier height (SBH, denoted by  $\varphi_{\rm B}$ ), we plot  $\ln(I_{\rm d}/$  $T^{3/2}$ ) versus 1000/T for various values of  $V_{\rm bg}$  as shown in Figure

4b,d for MoS<sub>2</sub>–G and MoS<sub>2</sub>–Ti, respectively. When  $V_{\rm d} \ge 3k_{\rm B}T/q$ ,

$$\ln\left(\frac{I_{\rm d}}{T^{3/2}}\right) = -\frac{q\left(\varphi_{\rm B} - \frac{V_{\rm d}}{n}\right)}{k_{\rm B}T} + \ln(A)$$

The effective SBH can be extracted from the slope of  $\ln(I_{\rm d}/T^{3/2})$  – 1/T and the n value we obtain from fitting the  $I_{\rm d}$  vs  $V_{\rm d}$  curves. The resulting values are shown in Figure 5. The excellent fitting over all the temperatures is evidenced by the small error bar values.

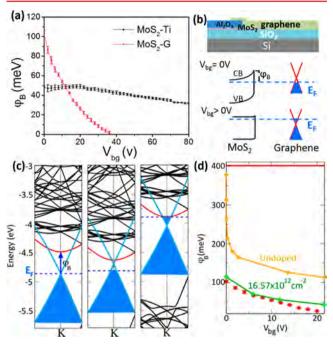

**Figure 5.** (a) Schottky barrier height  $\varphi_{\rm B}$  (in meV) and corresponding error bars, as a function of the gate bias  $V_{\mathrm{bg}}$  (in V) for CVD grown MoS<sub>2</sub>-G and MoS<sub>2</sub>-Ti junctions. (b) Experimental setup used (upper panel) and schematic band diagram of  $MoS_2/G$  heterostructure at  $V_{bg}$  = 0 and  $V_{\rm bg}$  > 0 (bottom panel). The corresponding edges of the valence band (VB) and the conduction band (CB) are shown, with  $E_F$  marked by the dashed line. (c) Calculated band structures of MoS<sub>2</sub>/graphene interface at zero bias and doping (left), zero bias with finite doping concentration  $(11.05 \times 10^{12} \text{ cm}^{-2})$  (middle) and 80 V back gate bias at the same doping (right).  $\varphi_B$  is indicated by the vertical arrow pointing from  $E_{\rm F}$  to the CB minimum at the K point. The relevant graphene and MoS<sub>2</sub> states are shown by blue and red lines, respectively. (d) Calculated  $\varphi_{\rm B}$  (in meV) as a function of the bias voltage  $V_{\rm bg}$  (in V) at different doping levels. The horizontal red line at 400 meV shows the value of the  $\varphi_{\rm B}$  expected from the difference between the work function of graphene (4.5 eV) and the electron affinity of MoS<sub>2</sub> (~4.1 eV). The red dots show the experimental results from (a).

In MoS<sub>2</sub>–G,  $\varphi_{\rm B}$  decreases dramatically from 110 to 0 meV with the back gate voltage changing from 0 to 35 V, as shown in Figure 5a. Previous studies have shown MoS<sub>2</sub>/graphene Schottky barriers ranging from 22 to 260 meV, depending on different gate voltage and sample preparation conditions. The barrier height in MoS<sub>2</sub>–Ti has relatively weak dependence with back gate voltage, changing from 50 to 40 meV with back gate changing from 0 to 80 V, as shown in Figure 5a. For an ideal metal semiconductor contact,  $\varphi_{\rm B}$  is determined by the difference between the work function of the metal  $(W_{\rm m})$ , the affinity of the semiconductor  $(\chi_{\rm s})$  and surface potential  $(\phi_{\rm s})$ , that is,  $\varphi_{\rm B} = W_{\rm m}$  –

$\chi_s + \phi_s$ . The change of  $\phi_B$  in MoS<sub>2</sub>–G comes from changes in both  $W_{\rm m}$  and  $\phi_s$ , as shown schematically in Figure 5b. In MoS<sub>2</sub>–Ti, the  $W_{\rm m}$  modulation is very limited, and the change in SBH is believed to come from the modulation of midgap interface states that impact  $\phi_s$ , just like in conventional metal—semiconductor junctions.

The work function of graphene can be modulated by electric field, following the expression:

$$W_{\rm m} = E_{\rm F} = -{\rm sgn}(n_0)\hbar\nu_{\rm F}\sqrt{\pi|n_0|}$$

,  $n_0 = q(V_{\rm bg} - V_{\rm t})$

where  $n_0$  is the carrier concentration in graphene,  $\hbar$  Planck's constant, and  $v_{\rm F}$  the Fermi velocity. <sup>41</sup> It was already found in the past that a change in the value of  $V_{\rm bg}$  by 30 V with 300 nm SiO<sub>2</sub> as back gate dielectric can cause a change of around 200 mV in graphene work function, <sup>41</sup> which is consistent with the change in the Schottky barrier height observed in our experimental data. As a result of this modulation, when the back gate voltage is larger than 35 V, the Schottky barrier height between MoS<sub>2</sub> and graphene is zero and an ohmic contact forms at the MoS<sub>2</sub> and graphene junction. Graphene outperforms Ti to contact MoS<sub>2</sub> with large carrier density which can be achieved using electronic doping or chemical doping. <sup>43</sup> The finite density of states and the tunability of its work function make graphene capable to form excellent contacts with MoS<sub>2</sub> and other semiconductors, offering new opportunities to design contact and to engineer junction interfaces. <sup>42</sup>

To elucidate some of the features of the MoS<sub>2</sub>-G heterostructure, we performed first-principles calculations using density functional theory (see Methods section for further details). Figure 5c shows the calculated band structure of the MoS<sub>2</sub>–G heterostructure for different doping and electric bias. In these calculations, we have considered only contact barriers which arise in the direction perpendicular to the 2D layers. The MoS<sub>2</sub>-G heterostructure has metallic character with the graphene Dirac cone from the dispersion of the  $p_z$  states falling within the MoS<sub>2</sub> band gap. The polarization of the electronic charge at the interface (see Figure S7 in Supporting Information) is stronger in graphene interfaces than in late transition metals, 41 which will be beneficial to the transfer of electrons from MoS<sub>2</sub> to graphene. Because of the very small density of states near the Fermi level (around the graphene Dirac point), the behavior of the device is sensitive to the position of  $E_{\rm F}$  inside of the band gap, which can be changed by electronic doping or external electric fields. At conditions of zero external bias and no doping (left panel in Figure 5c),  $E_{\rm F}$  is at the Dirac point and corresponds to small charge transfer (~0.01 electrons per cell from MoS<sub>2</sub> to graphene) and relatively weak interactions (~55 meV per C atom). At finite doping (middle panel in Figure 5c) or electric fields (right panel in Figure 5c),  $E_F$  is shifted away from the Dirac point, which changes the magnitude of the Schottky barrier height  $\varphi_{\rm B}$ . In this case, the barrier is given by the difference between the Fermi level of the combined system and the conduction band minimum of MoS2 at the k-point in the Brillouin zone. The results of barrier height change as a function of the external bias are shown in Figure 5d: At no doping and zero electric bias, the barrier height is 385 meV, close to the value of 400 meV obtained by simply calculating the difference between the graphene work function and the electron affinity of MoS<sub>2</sub>. In the real system, a small amount of doping will shift the value of  $\varphi_{\rm B}$  significantly from this value. When an external electric field is applied,  $\varphi_{\rm B}$  decreases monotonically with increasing values of the bias. The amount by which  $\varphi_{\rm B}$  changes depends on

the level of doping. The strong dependence of the value of  $\varphi_{\rm B}$  on the gate voltage, in the range  $0 < V_{\rm bg} < 2$  V is due to the very low density of states near the graphene Dirac point, as mentioned above, which results in large shift of the Fermi level for small amount of induced charge. For values of  $V_{\rm bg} > 6$  V, the change in  $\varphi_{\rm B}$  is smaller, and its slope is almost independent of the doping level at high concentrations ( $\sim 10^{13}$  cm $^{-2}$ , see Figure S8 in Supporting Information for different values of doping).

In summary, a novel 2D electronic system using heterostructures of single-layer MoS2 and graphene has been demonstrated where MoS2 serves as the channel material and graphene is used as both the ohmic and gate contacts, and the interconnects for the 2D electronic system. This technology represents the first large-scale platform for constructing electronics based on van der Waals heterostructures of 2D material monolayers. Both MoS<sub>2</sub> and graphene monolayers were grown using low-cost CVD methods, which are easily scalable to any size on arbitrary substrates. This work lays the foundation for a scalable all-2D-material electronics platform capable of taking full advantage of the mechanical flexibility and electrostatic integrity offered by monolayer electronic materials for applications in flexible and transparent electronics. Our systematic analysis of using graphene as contact material to interface with 2D semiconductors (in this study MoS<sub>2</sub>) for effective carrier injection into the channel, demonstrates that the tunable Fermi level offers unprecedented flexibility for matching the workfunction of the contacts with the channel. Combining the many advantages of graphene in high frequency electronics, 44-46 and its potential use as a new interconnect material superior to metals<sup>42,47</sup> at the nanometer scale,<sup>48</sup> the technological framework demonstrated in this work opens the door to many new opportunities for designing novel electronic systems.

**Methods.** Low-TALD. The low-temperature ALD deposition of  $Al_2O_3$  was performed on a commercial Savannah ALD system from Cambridge NanoTech at 100 °C using alternating cycles of  $H_2O$  and trimethylaluminum (TMA) as the precursors. The purge time between each cycle is 60 s to allow the full reaction.

AFM and Raman Spectroscopy. AFM for identifying the thin film thickness was performed on a Veeco Dimension 3100 system. Raman spectroscopy was performed with a 532 nm Nd:YAG laser. All optical micrographs were taken with a Zeiss Axio Imager.A1m microscope.

Device and Circuit Characterization. Device characterization was performed using an Agilent 4155C semiconductor parameter analyzer and a Lakeshore cryogenic probe station with micromanipulation probes. All measurements were done in vacuum ( $3 \times 10^{-6}$  Torr) at room temperature.

First-Principles Electronic Structure Calculations. The calculations reported here are based on density functional theory calculations using the SIESTA code. 49 The generalized gradient approximation<sup>50</sup> and nonlocal van der Waals density functional<sup>51</sup> was used together with double- $\varsigma$  plus polarized basis set, and norm-conserving Troullier-Martins pseudopotentials<sup>52</sup> to represent the atomic cores. The resolution of the real-space grid used to calculate the Hartree and exchange-correlation contribution to the total energy was chosen to be equivalent to 150 Ry planewave cutoff. Atomic coordinates were allowed to relax using a conjugate-gradient algorithm until all forces were smaller in magnitude than 0.01 eV/Å. To simulate the interface between graphene and MoS<sub>2</sub> layers, supercells containing up to 488 atoms were constructed using a graphene supercell of  $5 \times 5$  and a MoS<sub>2</sub> supercell of 4 × 4 that are approximately lattice matched in different stacking configurations. To avoid interactions between

layer images the distance between periodic images of the structures along the direction perpendicular to the surface was always larger than 20 Å. The number of k-points was chosen according to the Monkhorst–Pack<sup>53</sup> scheme, and was set to the equivalent of a 47 × 47 × 1 grid in the primitive unit cell of graphene, which gives well-converged values for all the calculated properties. We used a Fermi–Dirac distribution with an electronic temperature of  $k_{\rm B}T=21$  meV. The external electric field is introduced through a sawtooth-like electrostatic potential in the direction perpendicular to the MoS<sub>2</sub>–G plane. The different doping levels are obtained by adding a certain amount of electrons to the system and imposing a compensating uniform background in order to converge the total energy and the longrange Coulomb interactions.  $^{52,54}$

## ASSOCIATED CONTENT

## **S** Supporting Information

CVD growth of  $MoS_2$  and single layer graphene, alignment accuracy of fabrication process, top gate performances of  $MoS_2$ —G FET, temperature-dependence of  $MoS_2$ —Ti and  $MoS_2$ —G FETs, calculation of n and  $R_s$ , and DFT calculation of graphene/ $MoS_2$  interface. This material is available free of charge via the Internet at http://pubs.acs.org.

#### AUTHOR INFORMATION

### **Corresponding Authors**

\*E-mail: liliyu@mit.edu. \*E-mail: hw254@mit.edu. \*E-mail: tpalacios@mit.edu.

#### **Present Addresses**

\*Department of Chemical Engineering, Stanford University, Stanford, California 94305, United States, SLAC National Accelerator Laboratory, SUNCAT Center for Interface Science and Catalysis, Menlo Park, California 94025, United States.

△IBM T. J. Watson Research Center. Email: wanghan@us.ibm. com.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

The authors would like to thank Allen Hsu and Xu Zhang for their helpful advice on device fabrication and measurement. The authors acknowledge financial support from the Office of Naval Research (ONR) PECASE Program, the ONR GATE MURI program, the Army Research Laboratory, and Center for Integrated Quantum Materials (CIQM). This research has made use of the MIT's Microsystem Technology Laboratory cleanrooms. We acknowledge the use of computational resources provided by the Extreme Science and Engineering Discovery Environment (XSEDE), supported by NSF Grants TG-DMR120049 and TG-PHY120021.

# **■** REFERENCES

- (1) Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-layer MoS, transistors. *Nat. Nanotechnol.* **2011**, *6*, 147–150.

- (2) Liu, H.; Ye, P. D. Dual-Gate MOSFET With Atomic-Layer-Deposited as Top-Gate Dielectric. *IEEE Electron Device Lett.* **2012**, 33, 546–548.

- (3) Liu, H.; Neal, A. T.; Ye, P. D. Channel Length Scaling of MoS<sub>2</sub> MOSFETs. ACS Nano **2012**, *6*, 8563–8569.

- (4) Das, S.; Chen, H.-Y.; Penumatcha, A. V.; Appenzeller, J. High-Performance Multilayer MoS<sub>2</sub> Transistors with Scandium Contacts. *Nano Lett.* **2013**, *13*, 100–105.

(5) Fang, H.; et al. Degenerate n-Doping of Few-Layer Transition Metal Dichalcogenides by Potassium. *Nano Lett.* **2013**, *13*, 1991–1995.

- (6) Forrest, S. R. The path to ubiquitous and low-cost organic electronic appliances on plastic. *Nature* **2004**, 428, 911–918.

- (7) Dimitrakopoulos, C. D.; Mascaro, D. J. Organic thin-film transistors: A review of recent advances. *IBM J. Res. Dev.* **2001**, 45, 11–27.

- (8) Kim, D.-H.; et al. Complementary Logic Gates and Ring Oscillators on Plastic Substrates by Use of Printed Ribbons of Single-Crystalline Silicon. *IEEE Electron Device Lett.* **2008**, 29, 73–76.

- (9) Lee, G.-H.; et al. Flexible and Transparent MoS<sub>2</sub> Field-Effect Transistors on Hexagonal Boron Nitride-Graphene Heterostructures. *ACS Nano* **2013**, *7*, 7931–7936.

- (10) Yoon, J.; et al. Highly Flexible and Transparent Multilayer  $MoS_2$  Transistors with Graphene Electrodes. *Small* **2013**, n/a-n/a, DOI: 10.1002/smll.201300134.

- (11) Georgiou, T.; et al. Vertical field-effect transistor based on graphene-WS<sub>2</sub> heterostructures for flexible and transparent electronics. *Nat. Nano* **2013**, 8, 100-103.

- (12) Wang, H.; Hsu, A.; Wu, J.; Kong, J.; Palacios, T. Graphene-Based Ambipolar RF Mixers. *IEEE Electron Device Lett.* **2010**, 31, 906–908.

- (13) Lee, Y.; et al. Wafer-Scale Synthesis and Transfer of Graphene Films. *Nano Lett.* **2010**, *10*, 490–493.

- (14) Wang, H.; et al. Integrated Circuits Based on Bilayer MoS<sub>2</sub> Transistors. *Nano Lett.* **2012**, 12, 4674–4680.

- (15) Wang, H.; et al. Large-scale 2D electronics based on single-layer MoS<sub>2</sub> grown by chemical vapor deposition. *IEEE Int. Electron Devices Meet.* **2012**, 4.6.1–4.6.4, DOI: 10.1109/IEDM.2012.6478980.

- (16) Bertolazzi, S.; Krasnozhon, D.; Kis, A. Nonvolatile Memory Cells Based on MoS<sub>2</sub>/Graphene Heterostructures. *ACS Nano* **2013**, *7*, 3246–3252

- (17) Lee, Y.-H.; et al. Synthesis of Large-Area MoS<sub>2</sub> Atomic Layers with Chemical Vapor Deposition. *Adv. Mater.* **2012**, 24, 2320–2325.

- (18) Lee, Y.-H.; et al. Synthesis and Transfer of Single-Layer Transition Metal Disulfides on Diverse Surfaces. *Nano Lett.* **2013**, *13*, 1852–1857.

- (19) Mak, K.; Lee, C.; Hone, J.; Shan, J.; Heinz, T. Atomically Thin MoS\_{2}: A New Direct-Gap Semiconductor. *Phys. Rev. Lett.* **2010**, *105*, 136805.

- (20) Splendiani, A.; et al. Emerging photoluminescence in monolayer MoS<sub>2</sub>. *Nano Lett.* **2010**, *10*, 1271–1275.

- (21) Ramasubramaniam, A. Large excitonic effects in monolayers of molybdenum and tungsten dichalcogenides. *Phys. Rev. B* **2012**, *86*, 115409.

- (22) Berkelbach, T. C.; Hybertsen, M. S.; Reichman, D. R. Theory of neutral and charged excitons in monolayer transition metal dichalcogenides. *Phys. Rev. B* **2013**, *88*, 045318.

- (23) Berghäuser, G.; Malic, E. Analytical approach to excitonic properties of MoS<sub>2</sub>. *Phys. Rev. B* **2014**, *89*, 125309.

- (24) Lee, C.; et al. Anomalous Lattice Vibrations of Single- and Few-Layer MoS<sub>2</sub>. ACS Nano **2010**, *4*, 2695–2700.

- (25) Kuo, S.-W.; Kao, H.-C.; Chang, F.-C. Thermal behavior and specific interaction in high glass transition temperature PMMA copolymer. *Polymer* **2003**, *44*, 6873–6882.

- (26) Li, X.; et al. Large-Area Synthesis of High-Quality and Uniform Graphene Films on Copper Foils. Science 2009, 324, 1312–1314.

- (27) Bhaviripudi, S.; Jia, X.; Dresselhaus, M. S.; Kong, J. Role of Kinetic Factors in Chemical Vapor Deposition Synthesis of Uniform Large Area Graphene Using Copper Catalyst. *Nano Lett.* **2010**, *10*, 4128–4133.

- (28) Reina, A.; et al. Large Area, Few-Layer Graphene Films on Arbitrary Substrates by Chemical Vapor Deposition. *Nano Lett.* **2009**, *9*, 30–35.

- (29) Kim, K. S.; et al. Large-scale pattern growth of graphene films for stretchable transparent electrodes. *Nature* **2009**, *457*, 706–710.

- (30) Kim, S.; et al. High-mobility and low-power thin-film transistors based on multilayer MoS<sub>2</sub> crystals. *Nat. Commun.* **2012**, *3*, 1011.

- (31) Kang, J.; Sarkar, D.; Liu, W.; Jena, D.; Banerjee, K. A computational study of metal-contacts to beyond-graphene 2D semiconductor materials. *IEEE Int. Electron Devices Meet.* **2012**, 17.4.1–17.4.4, DOI: 10.1109/IEDM.2012.6479060.

(32) Popov, I.; Seifert, G.; Tománek, D. Designing Electrical Contacts to MoS\_{2} Monolayers: A Computational Study. *Phys. Rev. Lett.* **2012**, *108*, 156802.

- (33) Fuhrer, M. S.; Hone, J. Measurement of mobility in dual-gated MoS<sub>2</sub> transistors. *Nat. Nanotechnol.* **2013**, *8*, 146–147.

- (34) Dean, C. R.; et al. Boron nitride substrates for high-quality graphene electronics. *Nat. Nanotechnol.* **2010**, *5*, 722–726.

- (35) Liu, H.; et al. Statistical Study of Deep Submicron Dual-Gated Field-Effect Transistors on Monolayer Chemical Vapor Deposition Molybdenum Disulfide Films. *Nano Lett.* **2013**, DOI: 10.1021/nl400778q.

- (36) Kim, B.-J.; Shin, H.-A.-S.; Choi, I.-S.; Joo, Y.-C. Electrical failure and damage analysis of multi-layer metal films on flexible substrate during cyclic bending deformation. 2011 18th IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits 2011, 1–4, DOI: 10.1109/IPFA.2011.5992725.

- (37) Yu, W. J.; et al. Vertically stacked multi-heterostructures of layered materials for logic transistors and complementary inverters. *Nat. Mater.* **2013**, *12*, 246–252.

- (38) Pu, J.; et al. Highly Flexible  $MoS_2$  Thin-Film Transistors with Ion Gel Dielectrics. *Nano Lett.* **2012**, 12, 4013–4017.

- (39) Chang, H.-Y.; et al. High-Performance, Highly Bendable MoS<sub>2</sub> Transistors with High-K Dielectrics for Flexible Low-Power Systems. *ACS Nano* **2013**, *7*, 5446–5452.

- (40) Chen, J.-R.; et al. Control of Schottky Barriers in Single Layer  $MoS_2$  Transistors with Ferromagnetic Contacts. *Nano Lett.* **2013**, *13*, 3106–3110.

- (41) Yu, Y.-J.; et al. Tuning the Graphene Work Function by Electric Field Effect. *Nano Lett.* **2009**, *9*, 3430–3434.

- (42) Byun, K.-E.; et al. Graphene for True Ohmic Contact at Metal—Semiconductor Junctions. *Nano Lett.* **2013**, *13*, 4001–4005.

- (43) Shi, Y.; et al. Work Function Engineering of Graphene Electrode via Chemical Doping. ACS Nano 2010, 4, 2689–2694.

- (44) Han, W.; Nezich, D.; Jing, K.; Palacios, T. Graphene Frequency Multipliers. *IEEE Electron Device Lett.* **2009**, 30, 547–549.

- (45) Wang, H.; et al. BN/Graphene/BN transistors for RF applications. *IEEE Electron Device Lett.* **2011**, 32, 1209–1211.

- (46) Palacios, T.; Hsu, A.; Wang, H. Applications of graphene devices in RF communications. *IEEE Commun. Mag.* **2010**, *48*, 122–128.

- (47) Chen, X.; et al. Fully Integrated Graphene and Carbon Nanotube Interconnects for Gigahertz High-Speed CMOS Electronics. *IEEE Trans. Electron Devices* **2010**, *57*, 3137–3143.

- (48) Naeemi, A.; Meindl, J. D. Performance Benchmarking for Graphene Nanoribbon, Carbon Nanotube, and Cu Interconnects. *IEEE Int. Interconnect. Technol. Conf., Proc.* **2008**, 183–185, DOI: 10.1109/IITC.2008.4546961.

- (49) Soler, J. M.; et al. The SIESTA method for ab initio order-N materials simulation. *J. Phys.: Condens. Matter* **2002**, *14*, 2745.

- (50) Perdew, J. P.; Burke, K.; Ernzerhof, M. Generalized Gradient Approximation Made Simple. *Phys. Rev. Lett.* **1996**, *77*, 3865–3868.

- (51) Dion, M.; Rydberg, H.; Schröder, E.; Langreth, D. C.; Lundqvist, B. I. Van der Waals Density Functional for General Geometries. *Phys. Rev. Lett.* **2004**, *92*, 246401.

- (52) Troullier, N.; Martins, J. L. Efficient pseudopotentials for planewave calculations. *Phys. Rev. B* **1991**, 43, 1993–2006.

- (53) Monkhorst, H. J.; Pack, J. D. Special points for Brillouin-zone integrations. *Phys. Rev. B* **1976**, *13*, 5188–5192.

- (54) Makov, G.; Payne, M. C. Periodic boundary conditions in ab initio calculations. *Phys. Rev. B* **1995**, *51*, 4014–4022.