# MoS<sub>2</sub> FET Fabrication and Modeling for Large-Scale Flexible Electronics

Lili Yu, Dina El-Damak, Sungjae Ha, Shaloo Rakheja, Xi Ling, Jing Kong, Dimitri Antoniadis, Anantha Chandrakasan, Tomás Palacios Massachusetts Institute of Technology, Cambridge, MA 02139, U.S.A.

Tel: +1 (617) 460-7364, Fax: +1 (617) 258-7393, Email: liliyu@mit.edu, deldamak@mit.edu

#### **Abstract**

We present a state-of-the-art fabrication technology and physics-based model for molybdenum disulfide (MoS<sub>2</sub>) field effect transistors (FETs) to realize large-scale circuits. Uniform and large area chemical vapor deposition (CVD) growth of monolayer MoS<sub>2</sub> was achieved by using perylene-3,4,9, 10-tetracarboxylic acid tetrapotassium salt (PTAS) seeding. Then, a gate first process results in enhancement mode FETs and also reduces performance variation and enables better process control. In addition, a Verilog-A compact model precisely predicts the performance of the fabricated MoS<sub>2</sub> FETs and eases the large-scale integrated design. By using this technology, a switched capacitor DC-DC converter is implemented, and the measurement of the converter shows good agreement with the simulations.

Keywords: MoS<sub>2</sub>, 2D materials, large scale, flexible IC.

#### Introduction

MoS<sub>2</sub> has gained great interest for its atomic planar nature and mechanical flexibility to realize lightweight and flexible electronic systems on arbitrary surfaces. It has higher carrier mobility compared to amorphous Si and organic semiconductors and its 1.8eV bandgap allows high on-off ratio to construct low-cost flat-panel driving circuits [1]. Despite of its promising characteristics, applications up to date have been limited to single or a few devices scale system. The challenges in large-scale system design with a newly-introduced material mainly remain in three issues: material growth and transfer, device integration, and circuit simulations. First, a growth technology for large-area homogeneous monolayer MoS2 with large domain size and a low doping clean transfer is required. Second, enhancement mode FETs, with positive and reproducible threshold voltage (V<sub>T</sub>), are necessary to cascade logic circuits and complete a stand-alone system. For CVD MoS<sub>2</sub>, only depletion mode FETs [1,2] have been reported, which require external bias to drive other logic gates. Positive V<sub>T</sub> is hard to achieve due to the sensitivity of MoS2 to doping and the difficulty for dielectric integration. Lastly, earlier technologies lack computer-aided design

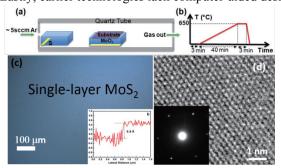

Fig. 1 (a) A schematic illustration of the  $MoS_2$  CVD system. (b) The temperature programming process used for a typical growth. (c) Optical micrographs and thickness profile (inset) of monolayer  $MoS_2$ . (d) HRTEM image and the corresponding selected area electron diffraction (SAED) pattern (inset) show the hexagonal crystal nature and the high quality lattice structure of  $MoS_2$ .

tools to facilitate the design of complex systems. In this paper, we address all these issues by using PTAS promoted CVD MoS<sub>2</sub> growth, gate-first fabrication process and Verilog-A compact model for circuit simulation.

#### **Material Growth**

Fig. 1(a) shows the experimental setup for the CVD synthesis of monolayer  $MoS_2$ , using S and  $MoO_3$  as the precursor, and PTAS as the seeding promoter. The furnace temperature profile during growth is shown in Fig. 1(b). An optical image of as-grown CVD  $MoS_2$  is shown in Fig. 1(c), demonstrating a good uniformity and a high coverage approaching 100%. The domain size of this sample is 30  $\mu$ m on average. The thickness is measured as 6.9 Å, a typical monolayer  $MoS_2$  thickness, using atomic force microscopy (Fig. 1(c), inset). The high quality of CVD-grown  $MoS_2$  is also evidenced by the highly ordered lattice structure observed under high resolution TEM as well as the crystal structure from diffraction pattern (Fig. 1(d)).

# **Device Fabrication**

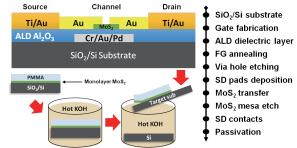

Next, device fabrication (Fig. 2) starts with gate patterning by photolithography and 5nm Cr/30 nm Au/30nm Pd metal stack deposition on a SiO<sub>2</sub> substrate. 20 nm Al<sub>2</sub>O<sub>3</sub> is then deposited using atomic layer deposition and annealed in forming gas for 30 minutes at 450°C to remove the fixed charge inside the dielectric. Via hole is patterned, followed by etching using reactive ion etching by Cl<sub>2</sub>/BCl<sub>3</sub> plasma. Then, as-grown MoS<sub>2</sub> CVD sample is coated with PMMA and soaked in hot KOH solution at 85°C. The SiO<sub>2</sub> layer is etched away and MoS<sub>2</sub>/PMMA stack is released then transferred to a new target substrate, followed by annealing process to clean the polymer residue. O<sub>2</sub> plasma is then used to isolate MoS<sub>2</sub> channel. Ohmic contacts and measurement pads of the devices/circuits are formed by depositing a 90 nm Au layer or 5nm Ti/90nm Au metal stack. Fig. 3 shows a top view of a test chip with different device components as well as circuits.

For conventional  $MoS_2$  FETs, with gate-last process, dielectric integration is usually conducted at low temperature or assisted by seeding layer, both resulting in fixed charge and trapped states inside the dielectric or at the interface. This causes extra scattering hence degradation of mobility as well as shift in  $V_T$ . Using the gate-first process instead, the critical components are fabricated before the  $MoS_2$  transfer step, achieving high gate dielectric and interface quality and the

Fig. 2 Fabrication technology for large scale MoS<sub>2</sub> electronics.

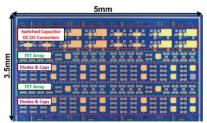

Fig. 3 Optical micrograph of the test chip fabricated using CVD grown monolayer MoS2, showing arrays of FETs, diodes and switched capacitor DC-DC converters

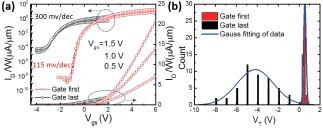

Fig. 4 (a) Transfer characteristics in linear (right y-axis) and log scale (left y-axis) and (b) Statistics of V<sub>T</sub> of MoS<sub>2</sub> FETs (channel length of 2um) from different fabrication technologies.

potential for low effective oxide thickness scaling. MoS<sub>2</sub> FETs with gate-first technology show larger V<sub>T</sub>, 10x larger on current, 100x smaller off current and steeper subthreshold slope (Fig. 4(a)) in comparison with gate-last based FETs. Devices from gate-first process have average V<sub>T</sub> of 0.54V with standard deviation of 0.12 V while those from gate-last process have average V<sub>T</sub> of -4.20 V and standard deviation of 1.75 V (Fig. 4(b)).

### Computer-Aided Design Flow for MoS<sub>2</sub> Technology

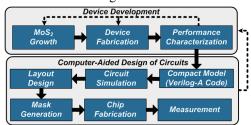

A complete computer-aided design (CAD) flow with device modeling, circuit simulation and parametric cell-based layout is developed in order to improve the design process of complex systems as shown in Fig. 5.

Fig. 5 Flow for large-scale MoS<sub>2</sub> integrated circuit development.

First, a drift diffusion Verilog-A compact (DDC) model is derived for the MoS<sub>2</sub> transistors. The model describes I-V characteristics of an FET, based on the electron transport properties of atomically thin MoS<sub>2</sub> substrates [3]. Given that the current in a FET is simplified as

$$I_D = \frac{1}{2}W(Q_{is} + Q_{id})f(v_{sat})v_{sat},$$

(1)

where W is the device width, Qis and Qid are the channel charges at source and drain, respectively, and v<sub>sat</sub> is the satu-

ration velocity of carrier. The

$$f(v_{sat})$$

is given by

$$f(v_{sat}) = \frac{(Q_{is} - Q_{id})/C_{invi}V_{DSAT}}{(1 + ((Q_{is} - Q_{id})/C_{invi}V_{DSAT})^{\beta})^{1/\beta}},$$

(2)

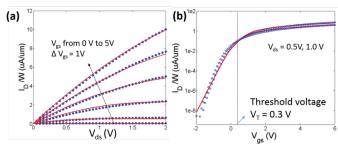

where  $C_{invi}$  is the channel-to-gate capacitance, and  $\beta$  is an empirical parameter that can be obtained from experimental data. Fig. 6 depicts the modeled I-V characteristics with the measurement data from a MoS2 FET.

Fig. 6 I-V curves of a MoS<sub>2</sub> FET from DDC model (line) and measurement (dots).

With the parameters extracted from FETs, the DDC model is implemented in Verilog-A language to enable circuit simulation as in standard silicon ASIC design process. Lastly, the FET layout is implemented in a parametric cell to ease the layout of large-scale system designs.

## **Switched Capacitor DC-DC Converter**

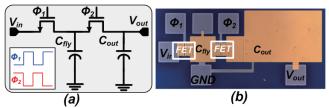

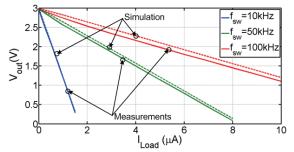

A switched capacitor DC-DC converter is implemented using the CAD flow. The converter consists of two MoS<sub>2</sub> switches and a charge transfer capacitor,  $C_{fly}$  as shown in Fig. 7(a). As shown in Eq. (3), the output voltage of the converter,  $V_{out}$ , is a function of  $V_{in}$ ,  $I_{out}$  and  $f_{sw}$  where  $I_{out}$  is the output current and  $f_{sw}$  is the converter switching frequency [4].

$$V_{out} = V_{in} - \frac{I_{out}}{C_{fly} f_{sw}} \tag{3}$$

In this implementation,  $C_{fly}$  is 56pF, and the switch size is 40μm/2μm. Fig. 7(b) shows the micrograph of the fabricated converter. The gates of the switches are driven externally with 0-5V swing control signals that are 180° out-of-phase as shown in Fig. 7(a), while the input is kept 3V. The measurement of the output voltage while varying load current and switching frequency matches well with the simulation as shown in Fig. 8.

Fig. 7 (a) Schematic diagram of the switched capacitor converter and (b) micrograph of the fabricated converter.

Fig. 8 Simulation (dotted) and measurements (solid) of the output voltage versus the load current of MoS<sub>2</sub> SC DC-DC converter.

### Acknowledgments

This work is supported by CIQM, ONR PECASE, SRC and CICS.

# References

- [1] H. Wang, et al., Nano Lett., 12(9), pp 4674-4680, 2012

- [2] L.Yu, et al., Nano Lett., 14(6), pp 3055-3063, 2014

- [3] S. Rakheja, et al., IEDM 2013

- [4] Y. Ramadass, et al., IEEE JSSC, pp 2557-2565, 2010