# High-Performance WSe<sub>2</sub> Complementary Metal Oxide Semiconductor Technology and Integrated Circuits

Lili Yu,\*,† Ahmad Zubair,† Elton J. G. Santos,‡ Xu Zhang,† Yuxuan Lin,† Yuhao Zhang,† and Tomás Palacios\*,†

ABSTRACT: Because of their extraordinary structural and electrical properties, two-dimensional materials are currently being pursued for applications such as thinfilm transistors and integrated circuit. One of the main challenges that still needs to be overcome for these applications is the fabrication of air-stable transistors with industry-compatible complementary metal oxide semiconductor (CMOS) technology. In this work, we experimentally demonstrate a novel high performance air-stable WSe2 CMOS technology with almost ideal voltage transfer characteristic, full logic swing and high noise margin with different supply voltages. More importantly, the inverter shows large voltage gain (~38) and small static power (picowatts), paving the way for low power electronic system in 2D materials.

KEYWORDS: Transition metal dichalcogenides, integrated circuits, complementary logic, CMOS electronics, air stable doping, low power electronics

wo-dimensional (2D) crystals, including graphene, hexagonal boron nitride, and transition metal dichalcogenides (TMD), have outstanding properties for developing the next generation of electronic devices. 1-7 Their extreme thinness, down to a single layer, allows almost perfect electrostatic control of the transistor channel, making them robust to short channel effects and ideal for low power applications.<sup>8</sup> In addition, these materials offer excellent mechanical flexibility, optical transparency, and favorable transport properties for realizing electronic, sensing, and optical systems on arbitrary surfaces. 9-12 These thin, lightweight, bendable, highly rugged, and low-power devices could bring dramatic changes to information processing, communications, and human-electronic interaction. One of the main challenges that still needs to be overcome for these applications is the fabrication of air-stable transistors with industry-compatible complementary metal oxide semiconductor (CMOS) technology. 13,14 CMOS logic has high noise immunity, well-established circuit designs, low static power consumption, and high density of integration.15

CMOS is made from complementary and symmetrical pairs of p-type and n-type metal oxide semiconductor field effect transistors (MOSFETs) with matched threshold voltage and current level. CMOS logic circuits on two-dimensional (2D) materials have first been demonstrated on structures with two different layered materials, where one material is used for the ntype MOSFET (nMOS) device and a different material system is used for the p-type MOSFET (pMOS). 16,17 Logic inverters

have been fabricated with this heterogeneous combination, however these logic gates showed small gain (less than 2) and unmatched input output voltage, leading to zero noise margin. 16,17 To achieve a single-2D-material CMOS technology, WSe2 is arguably a more promising semiconductor than the more explored MoS2 because of the more balanced conduction and valence band edges to different work functions metals and symmetric electron and hole effective mass. An integrated WSe2 CMOS technology has been demonstrated using gas-phase doping.<sup>13</sup> The device shows however short lifetime in air, and the absence of rail-to-rail performance indicates significant static leakage current between the supply line and ground, which leads to large power consumption. More recently, an electrostatically doped WSe<sub>2</sub> CMOS technology has been reported, however extra terminals and multiple voltage bias supplies are needed, which significantly increases the circuit complexity.<sup>14</sup> Hence, to the best of our knowledge there is still no report of an integrated 2D CMOS technology that is stable and offers high-enough noise margin for actual applications.

In this Letter, we experimentally demonstrate an air-stable novel high performance WSe2 CMOS technology with excellent voltage transfer characteristic, full logic swing and high noise margin. More importantly, the inverter shows high

Received: February 17, 2015 Revised: July 17, 2015 Published: July 20, 2015

Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, 77 Massachusetts Avenue, Cambridge, Massachusetts 02139, United States

<sup>\*</sup>Department of Chemical Engineering, Stanford University, Stanford, California 94305, United States

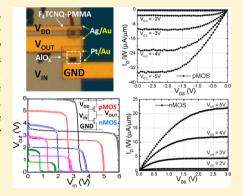

Figure 1. Structure, doping method, and band alignment. (a) Sechematic and (b) optical image of device structure of WSe<sub>2</sub> CMOS technology with  $F_4TCNQ$ -PMMA doped pMOS and  $AlO_x$  encapsulated nMOS. The source electrode of the nMOS and pMOS transistors are connected to ground and  $V_{dd}$  power supply, respectively. Their gates are connected with each other as the input node while the drains are connected to serve as the output node. (c) Localized and air-stable p type doping method for WSe<sub>2</sub> using  $F_4TCNQ$ -PMMA mixture. (d) Band diagram in the CMOS system.

voltage gain and static power consumption as low as pico-watts, paving the way for ultralow power system in 2D materials.

Figure 1a shows the schematic of the device structure used in this work. nMOS and pMOS transistors are monolithically integrated on a single WSe2 flake. The device fabrication starts with gate patterning and 5 nm Cr/30 nm Au/30 nm Pd metal stacks deposition on a SiO<sub>2</sub> substrate. Then 20 nm Al<sub>2</sub>O<sub>3</sub> is deposited using atomic layer deposition (ALD) on the gate electrode. A 30 min forming gas annealing at 450 °C is then applied to remove the fixed charge inside the dielectric. The thin ALD dielectric layer provides good electrostatic control of the gate, and matched voltages of source/drain and gate. Atomically thin WSe<sub>2</sub> flakes are achieved via micromechanical exfoliation and then transferred on to the gate stack (see Methods section), followed by high-temperature annealing to clean the polymer residue. Then a low work function metal (i.e., Ag) and a high work function metal (i.e., Pt) are used to contact the nMOS and pMOS FETs (Figure 1c), respectively. The nMOS is then covered with AlO<sub>x</sub> before p-doping (see Methods section for details). To improve the pMOS performance, tetrafluoro-tetracyanoquinodimethane  $(F_4TCNQ)^{18,19}$  is used to dope the WSe<sub>2</sub> channel, which helps to reduce the pMOS Schottky barrier width and also to increase the tunneling hole current. To increase the long-term stability of F<sub>4</sub>TCNQ, we incorporated it into a F<sub>4</sub>TCNQ-Poly(methyl methacrylate) (PMMA) mixture by using Anisole as a solvent (Figure 1c) with different weight ratio of F<sub>4</sub>TCNQ. The solution is spin-coated on the sample and the F<sub>4</sub>TCNQ molecules are trapped in the PMMA polymer chain network. Then electron beam lithography is used to expose the F<sub>4</sub>TCNQ-PMMA mixture where the nMOS devices will be located, following by development using MIBK/IPA developer to remove the F<sub>4</sub>TCNQ-PMMA mixture in those regions. As a result, the doping is localized only in pMOS where F<sub>4</sub>TCNQ-PMMA left. Charge transfer happens between the F<sub>4</sub>TCNQ-PMMA layer and the WSe<sub>2</sub> underneath it, achieving localized ptype doping. Figure 1b is the optical image of the final integrated CMOS inverter on WSe $_2$  flake. Figure 1d shows the work function alignment of contact metal (Ag, Pt), oxide (Al $_2$ O $_3$ ), semiconductor band diagram (WSe $_2$ ) and acceptor molecule energy level (F $_4$ TCNQ) in this CMOS technology. The highest occupied molecular orbital energy of F $_4$ TCNQ is lower than the valence band edge of WSe $_2$ , which induces the transfer of electrons from WSe $_2$  to F $_4$ TCNQ, resulting p doping in WSe $_2$ , which will be discussed in detail later. High/low work function metals are deliberately chosen to help the charge injection of hole and electron, respectively. It should be noted that the maximum current of the nMOS devices does not show any change after process steps of AlO $_x$  deposition, F $_4$ TCNQ-PMMA coating, writing, and development.

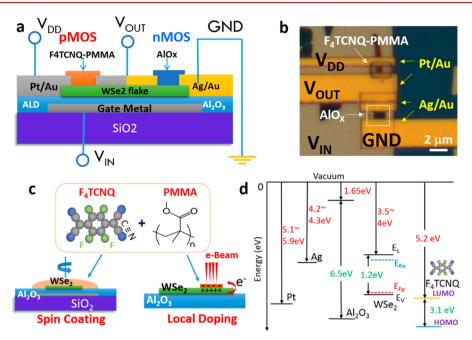

The transfer characteristics of WSe<sub>2</sub> nMOS transistors with a Ag/Au metal stack contact on an Al<sub>2</sub>O<sub>3</sub> substrate are shown with a black line in Figure 2a. There is a highly conductive electron current and suppressed hole current, with high on-off ratio close to 108. In our experiment, WSe<sub>2</sub> flakes exfoliated on top of SiO<sub>2</sub> usually show ambipolar performance with slightly higher hole branch current (inset, Figure 1a), while flakes on Al<sub>2</sub>O<sub>3</sub> substrate (such in our devices, where Al<sub>2</sub>O<sub>3</sub> is used as gate dielectric) without forming gas annealing show degenerate electron doping (red dashed line in Figure 1 a). The doping comes from the fixed charge on the surface or in the bulk of the dielectric layer or interaction between the 2D material and the substrate, which has been previously observed in both graphene<sup>20,21</sup> and MoS<sub>2</sub><sup>22</sup> on different substrates. The positive fixed charge causes charged impurity scattering in WSe2, which degrades mobility and makes it difficult to turn off the device. Thus, high-temperature annealing is needed to improve the dielectric quality without degrading material quality as well as to tune the nMOS threshold voltage. In order not to damage the WSe<sub>2</sub> layer during the high-temperature annealing, we developed a gate metal/dielectric stack-first fabrication process,

**Figure 2.** Effect of contact metals and dopants. (a) Transfer characteristics of Ag-contacted WSe<sub>2</sub> FET on Al<sub>2</sub>O<sub>3</sub> substrate with (black solid line) and without (red dashed line) gas annealing treatment. Inset, Ag-contacted WSe<sub>2</sub> FET on SiO<sub>2</sub> substrate. Fixed charge in the dielectric layer has an important doping effect. (b) Transfer characteristics of Pt-contacted WSe<sub>2</sub> FET with different concentration of F<sub>4</sub>TCNQ. When F<sub>4</sub>TCNQ concentration in PMMA increases, the hole current increases while the electron density significantly decreases. (c) Long-term stability of pMOS fabricated by three different doping methods. Device doped by 10% F<sub>4</sub>TCNQ/PMMA mixture shows almost no current change after 2 weeks; device doped by 2% F<sub>4</sub>TCNQ/IPA solution shows 30% current decrease after 2 weeks, while device doped by NO<sub>2</sub> gas shows 20 times current reduction after only 1 day.

which allows the transfer of the WSe<sub>2</sub> layer after the gate dielectric has been annealed at high temperature.

The transfer characteristics of pMOS WSe<sub>2</sub> transistors with a Pt ohmic contact technology on an Al<sub>2</sub>O<sub>3</sub> substrate are shown in Figure 2b (red dash-dot line). Opposite to the Ag/Au contacted nMOS device, this device exhibits ambipolar performance with low electron and hole current. To increase the hole-based current, F<sub>4</sub>TCNQ is used to dope the channel. This molecule has been reported to be an effective p-type dopant in single-wall carbon nanotubes field effect transistors as well as organic semiconductors such as zinc-phthoalocyaniene (ZnPc).<sup>23</sup> The transfer characteristics of WSe<sub>2</sub> FETs

doped by different concentration of  $F_4TCNQ/PMMA$  solution are shown in Figure 2b. The hole current of the device increases, the electron current decreases, and the threshold voltage also decreases as the  $F_4TCNQ$  concentration increases. With 10%  $F_4TCNQ$  in PMMA, the hole current increases by more than 1000× while the electron current decrease more than 6 orders of magnitude than that of devices before doping.

The long-term stability of the new F<sub>4</sub>TCNQ/PMMA localized doping was also studied and compared with other p-doping methods, as shown in Figure 2c. After 2 weeks exposure to air, the on-state hole current does not change while the current increases slightly in the subthreshold region. These results are significantly more stable than with other doping methods traditionally used in the literature, for example, exposure to strong oxidizing NO<sub>2</sub> gas<sup>24</sup> or directly coating with F<sub>4</sub>TCNQ/IPA solution (see Methods section for details). For the NO<sub>2</sub> gas doping, the hole current drops by more than 20 times in the first 24 h, while for pure F<sub>4</sub>TCNQ (2% in IPA) doping, the current decreases by 30% after 2 weeks. F<sub>4</sub>TCNQ has been found to be unstable and volatile, especially at elevated temperature, <sup>25</sup> because of its diffusion properties, thus PMMA scaffold effectively stabilize F<sub>4</sub>TCNQ on WSe<sub>2</sub> surface.

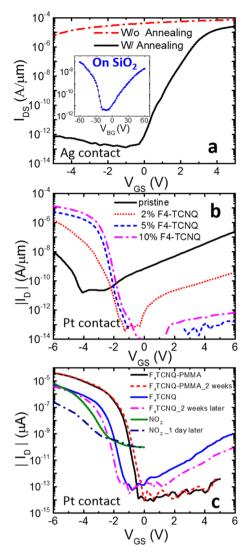

After optimizing the substrate, metal contacts, and dopants, we achieve simultaneously high-performance nMOS and pMOS FETs, whose transport performance are shown in Figure 3. The WSe<sub>2</sub> flake has a thickness of 5 nm and the nMOS/pPMOS transistors have a channel length of 1  $\mu$ m. From the transfer characteristics, they are both enhancement mode transistors with high on/off ratio (10<sup>7</sup> for nMOS and 10<sup>8</sup> for pMOS). The threshold voltage for the nMOS and pMOS devices are 2 and -1.8 V, respectively, while the subthreshold swings are 167 and 162 meV/dec The devices show a linear current behavior at low drain bias voltages and excellent current saturation at higher drain biases with on-state current density of 22 and 35  $\mu$ A/ $\mu$ m in nMOS and pMOS transistors, respectively. The conservative estimation (including contact resistance) of mobility for electrons and holes are 27.4 and 42.6  $\mbox{cm}^2\,\mbox{V}^{-1}\,\mbox{s}^{-1}$  , respectively. In a field effect transistor, the effective channel length is shortened with increasing in drain bias beyond saturation. This phenomena, known as channel length modulation, is typically characterized through the parameter  $\lambda$ in the drain current expression (nMOS as an example)  $I_D$  =  $[(uC_{ox}W)/(2L)][(V_{GS} - V_{TN})^2(1 + \lambda V_{DS})]$ , where  $\mu$  is the carrier mobility,  $C_{\rm ox}$  is the gate capacitance, W and  $\dot{L}$  are the device width and length,  $V_{\rm GS}/V_{\rm DS}$  is the gate/drain voltage, and  $V_{

m TN}$  is the threshold voltage of nMOS, respectively. From Figure 3b,d, both the nMOS and the pMOS transistors have very small channel length modulation. Therefore, the output resistance  $r_0 = (\partial I_{\rm D}/\partial V_{\rm DS})^{-1} = (\lambda I_{\rm D})^{-1}$  is large. This is very important to achieve high gain in inverter or amplifier, which is proportional to  $r_0$ .

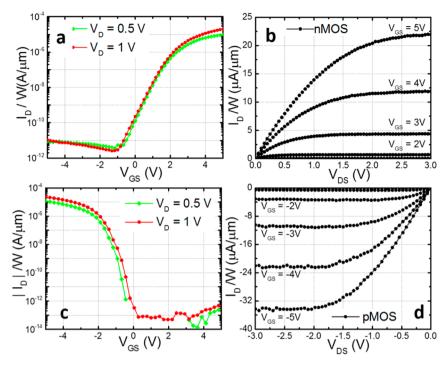

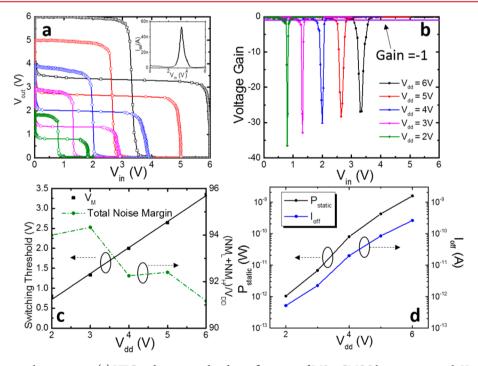

The nMOS and pMOS technologies described above were used to fabricate an integrated CMOS logic inverter (Figure 1a). The voltage transfer characteristics (VTC) of the fabricated CMOS inverter are shown in Figure 4a. The WSe<sub>2</sub> CMOS inverter shows excellent inverting performance under a wide range of  $V_{\rm dd}$  values, 2 to 6 V, which gives full logic swing, abrupt transition, symmetrical shape and high noise margin. In addition, there is almost zero current under static conditions (Figure 4a, inset). The sharp transition between the two logic states can be characterized by the voltage gain  $A_{\rm v} = dV_{\rm out}/dV_{\rm in}$  (Figure 4b). As shown in Figure 4b, the gain is close to zero, except at the transition region where the gain experiences a

Figure 3. Transfer and output characteristics of transistors.  $WSe_2$  nMOS (a) transfer characteristics and (b) output characteristics;  $WSe_2$  pMOS (c) transfer characteristics and (d) output characteristics. Both transistors show high on–off ratio, high on current density, and excellent current saturation.

Figure 4. Integrated circuit characteristics. (a) VTC and corresponding butterfly curves of WSe<sub>2</sub> CMOS logic inverter with  $V_{\rm dd}$  supply from 2 to 6 V. Inset: current change with input voltage. (b) Voltage gain of WSe<sub>2</sub> CMOS logic inverter, gain equaling to -1 is denoted by the purple line, the peak gain decrease with the increase of  $V_{\rm dd}$  value. (c) Switching threshold (left axis) and ratio of total noise margin (right axis) to  $V_{\rm dd}$  as a function of  $V_{\rm dd}$ . (d) Static power consumption (left axis) and off current (right axis) of the CMOS inverter as a function of  $V_{\rm dd}$ .

sharp peak at half  $V_{\rm dd}$  voltage, with a maximum value of 38 for  $V_{\rm dd}=2$  V. A gain larger than 1 is important for cascade logic application because it makes the circuit regenerative and robust to errors, which is very important for multistage logic applications. When  $V_{\rm dd}$  decreases, the peak gain increases and the transition region becomes narrower. From a small signal

model of an inverter, the voltage gain can be calculated using  $A=(g_{\rm mn}+g_{\rm mp})(r_{\rm op}||r_{\rm on})=[(\lambda_{\rm n}+\lambda_{\rm p})(V_{\rm g}-V_{\rm Tn})]^{-1}\propto (V_{\rm dd}/2-V_{\rm Tn})^{-1}$ , thus the gain decreases with increasing  $V_{\rm dd}$ . In previous work, <sup>13</sup> researchers showed the opposite trend, which may indicate that the device performance is unstable with significant current leakage between the power supply and ground, which

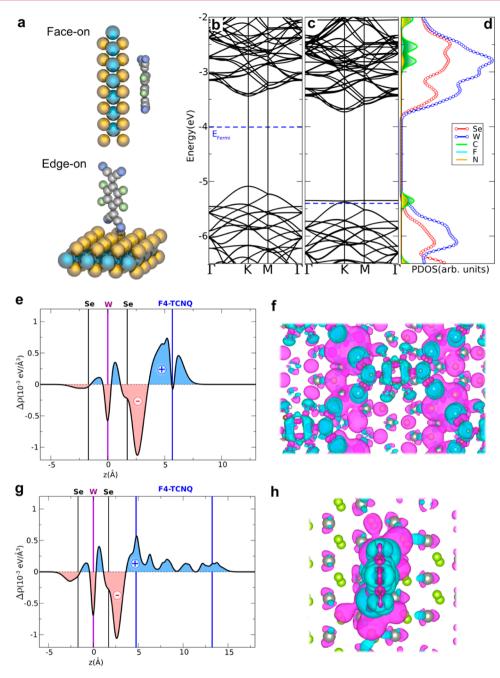

Figure 5. First principle calculations. P-type behavior induced by  $F_4$ -TCNQ on WSe<sub>2</sub> layers. (a) Molecular structures of  $F_4$ -TCNQ on top of WSe<sub>2</sub> at face-on and edge-on geometries. (b,c) Calculated band structure of pristine WSe<sub>2</sub> and face-on interface, respectively. (d) Projected density of states (PDOS) on different atoms of the system at face-on geometry on the valence states used in the calculation for each specie. (e,g) Plane-averaged electron density difference along the direction perpendicular to the interface of face-on and edge-on structural configurations, respectively. The blue and red colors indicate electron accumulation and depletion. (f,h) Top views of the charge density differences between  $F_4$ -TCNQ and WSe<sub>2</sub> systems at face-on and edge-on interfaces, respectively. The iso-surfaces are at  $1.4 \times 10^{-3}$  e/Å<sup>3</sup>. Red means charge depletion and blue is charge accumulation.

prevents the static output voltage from reaching the supply voltage. The stable doping technology adopted in this paper makes the device scale properly with  $V_{\rm dd}$ , offering a wide range of operating biasing conditions to match the power requirements of each particular application.

The switching threshold (SW, the voltage at which the output voltage is the same as the input voltage) and noise margin are important parameters for device robustness. SWs for our WSe<sub>2</sub> inverter are plotted as a function of  $V_{\rm dd}$  in Figure 4c. It is linear with  $V_{\rm dd}$  with a slope close to 0.5. The total noise

margin of the inverter is higher than 90% of  $V_{\rm dd}$ , which shows the large tolerance of the device to intrinsic or extrinsic noise. This large noise margin, together with matched input—output, high gain, makes our devices easy to be integrated into multistage large system.

Finally, the biggest advantage of CMOS technology is the power consumption. The power is typically divided in dynamic and static power. Static power can be expressed as  $P_{\rm static} = V_{\rm dd}(I_{\rm static\_low} + I_{\rm static\_high})/2$  at static state  $(V_{\rm in} = 0 \text{ V or } V_{\rm in} = V_{\rm dd})$  while the dynamic power is proportional to  $V_{\rm dd}^2$  and will

not be discussed here. The static current and the power consumption, averaged at high and low state, under different  $V_{\rm dd}$  values for our integrated logic inverter are plotted in Figure 4d. The current increases with  $V_{\rm dd}$  exponentially, because of the tunneling nature of leakage current under static operation. The static power consumption reaches 2 pW when  $V_{\rm dd}$  is 2 V. This is at least orders of magnitude lower than previous work where the static power is roughly estimated to be in the hundred nanowatts range for  $V_{\rm dd}$  of 3 V. This demonstrates the high potential of WSe<sub>2</sub> CMOS technology for ultralow power electronics.

To further understand the doping effect of F<sub>4</sub>TCNQ on WSe2, we performed first-principles calculations using density functional theory, including van der Waals interactions (see Methods section for further details). We considered supercells composed of F<sub>4</sub>TCNQ molecules at two different molecular configurations as shown in Figure 5a. It was found that the configurations where F<sub>4</sub>TCNQ molecules lie down on WSe<sub>2</sub> layers (face-on) bind stronger than those where the molecules assume a tilted orientation (edge-on). The energy difference is as large as 0.11 eV per F<sub>4</sub>TCNQ molecule that points to a potential preferential orientation at the interface. Even though the binding energies are different, the electronic structure of both geometries shows similar features. The calculated band structures, including van der Waals dispersion forces of WSe2 layers before and after the doping at face-on geometry are shown in Figure 5a,b, respectively. Similar results are obtained for edge-on geometry (not shown). The adsorption of F<sub>4</sub>TCNQ induces the appearance of extra-hole energy levels near the top of the valence band of WSe2, mainly composed by s and p states from C atoms at the molecule, with smaller contribution from N (Figure 5d). A charge transfer of 0.25 electrons per unit cell is observed from WSe2 to F4TCNQ, which induces a shift to lower energies of the Fermi level (Figure 5b). This explains the F<sub>4</sub>TCNQ p-type doping behavior in WSe2, which remarkably agrees with the experimental measurements discussed above. The charge transfer between WSe2 and F4TCNQ also creates an interfacial dipole moment of 2.94 and 7.02 D at face-on and edge-on configurations, respectively. This is observed mainly at the first Se-layer closer to the F<sub>4</sub>TCNQ molecules (Figure 5e,g). The charge density differences for face-on (Figure 5f) and edge-on (Figure 5h) interfaces point to a higher charge depletion at the WSe<sub>2</sub> layer between the F<sub>4</sub>TCNQ molecules and at the N atoms, where the molecules stand up. These results strongly suggest that F4TCNQ on top of WSe2 can be used as an effective p-type dopant in WSe<sub>2</sub>.

In conclusion, we report a high-performance CMOS technology in WSe2. We systematically study the effect of metal contact, the substrate and the acceptor doping to the performance of WSe<sub>2</sub> devices. High on-off ratio, high current density, and excellent current saturation are achieved in both nMOS and pMOS transistors. By fabricating CMOS inverters, we show that this technology presents excellent voltage transfer characteristic, full logic swing and high noise margin, which is stable in the air. More importantly, the inverter shows large voltage gain (~38), total noise margin larger than 90% of operating voltage, small static power (picowatts). We expect that the air-stable, noise-robust, high-gain, and low-power CMOS technology presented in this paper can be easily applied to larger circuits in the near future, thanks to the fast progress in large scale CVD WSe<sub>2</sub> growth. 26 This work therefore paves the way for ultralow power system in 2D materials.

**Methods.** ALD. The low-temperature ALD deposition of  $Al_2O_3$  was performed on a commercial Savannah ALD system from Cambridge NanoTech at 250 °C using alternating cycles of  $H_2O$  and trimethylaluminum (TMA) as the precursors.

Dry Transfer. The WSe<sub>2</sub> was micromechanically exfoliated from commercially available bulk natural crystal (Nanosurf) on a previously prepared transfer slide using cleanroom grade lowtack tapes.<sup>27</sup> The transfer slide consisted of a supporting stack of transparent materials and a polymer release layer. The supporting stack was made of glass/Sylgard 184 polydimethylsiloxane (PDMS)/clear packing tape and the polymer release layer was a double layer of methyl methacrylate (MMA). Small squares of WSe2/MMA/tape/PDMS stack were then cut out using a sharp clean blade and transferred on another clean glass slide. The glass slide and prepatterned substrate were then mounted on the in-house alignment transfer setup, consisting of an optical microscope and micromanipulator. The target flake and substrate with gate pattern were carefully aligned and engaged in contact with stage temperature of 35  $^{\circ}$ C. The stage was then heated to 130  $^{\circ}$ C and the glass slide disengaged from the target substrate. At the same time, MMA with WSe<sub>2</sub> flakes was released from tape/PDMS/ glass stack and successfully transferred to the gate pattern. The sample was then soaked in acetone and annealed at 200 °C in Ar/H<sub>2</sub> to remove the polymer residue from the transfer process.

*AFM.* Atomic force microscopy (AFM) for identifying the thin film thickness was performed on a Veeco Dimension 3100 system.

nMOS Passivation. PMMA on top of nMOS region was exposed by electron beam lithography, followed by development. Then Al metal was deposited and exposed to air for oxidization for three times to get the desired thickness with 1.5 nm thick Al each time. Then the sample was heated on a hot plate in air for several hours at 100 °C for full oxidization.

$NO_2$  gas and  $F_4TCNQ/IPA$  Doping. For  $NO_2$  gas doping, the sample was exposed to  $NO_2$  gas for several minutes for  $WSe_2$  to absorb  $NO_2$  gas on its surface. For  $F_4TCNQ/IPA$  doping,  $F_4TCNQ$  was first mixed into IPA solution by weight ratio and then the solution was coated onto the  $WSe_2$  device. Pure  $F_4TCNQ$  was left on the sample surface after IPA evaporates.

Device and Circuit Characterization. Device characterization was performed using an Agilent 4155C semiconductor parameter analyzer and a Lakeshore cryogenic probe station with micromanipulation probes. All measurements were done in vacuum ( $3 \times 10^{-6}$  Torr) at room temperature.

First-Principles Calculations. Calculations were based on ab initio density functional theory using the SIESTA code.<sup>28</sup> The generalized gradient approximation<sup>29</sup> and nonlocal van der Waals density functional<sup>30</sup> were used together with double- $\zeta$ plus polarized basis set, norm-conserving Troullier-Martins pseudopotentials.<sup>31</sup> Atomic coordinates were allowed to relax using a conjugate-gradient algorithm until all forces were smaller in magnitude than 0.01 eV/Å. Relevant lattice constants (in-plane and out-of-plane) were optimized for each system. To avoid interactions between supercell images the distance between periodic images of the F<sub>4</sub>TCNQ/WSe<sub>2</sub> structures along the direction perpendicular to the WSe2-plane was always larger than 20 Å. The resolution of the real-space grid used to calculate the Hartree and exchange-correlation contribution to the total energy was chosen to be equivalent to 150 Ry planewave cutoff. The number of *k*-points was chosen according to the Monkhorst–Pack scheme<sup>32</sup> and was set to the equivalent of

a 45  $\times$  45  $\times$  1 grid in the primitive unit cell of WSe<sub>2</sub>, which gives well converged values for all the calculated properties. We used a Fermi–Dirac distribution with an electronic temperature of  $k_{\rm B}T=21$  meV.

## AUTHOR INFORMATION

#### **Corresponding Authors**

\*E-mail: liliyu@mit.edu. \*E-mail: tpalacios@mit.edu.

## **Author Contributions**

T.P. and L.Y. conceived and supervised the research. L.Y. and A.Z. fabricated the device. L.Y. performed the measurements and data analysis. E.J.G.S. performed the van der Waals first-principles simulations. X.Z., Y.L., and Y.Z. helped with fabrication process. L.Y. and T.P. cowrote the manuscript. All authors commented on the manuscript and discussed the results.

#### **Notes**

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

The authors would like to thank Allen Hsu and Amir Nourbakhsh for their helpful advice on device fabrication and measurement. This work was supported by the STC Center for Integrated Quantum Materials, NSF Grant DMR-1231319. The authors also acknowledge financial support from the Army Research Laboratory (Dr. Madan Dubey), the Office of Naval Research (ONR) PECASE Program (Dr. Paul Maki). This research has made use of the MIT's Microsystem Technology Laboratory cleanrooms. We acknowledge the use of computational resources provided by the Extreme Science and Engineering Discovery Environment (XSEDE), supported by NSF Grants TG-DMR120049 and TG-PHY120021.

# REFERENCES

- (1) Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-layer MoS2 transistors. *Nat. Nanotechnol.* **2011**, *6*, 147–150.

- (2) Fiori, G.; et al. Electronics based on two-dimensional materials. *Nat. Nanotechnol.* **2014**, *9*, 768–779.

- (3) Ferrari, A. C.; et al. Science and technology roadmap for graphene, related two-dimensional crystals, and hybrid systems. *Nanoscale* **2015**, *7*, 4598–4810.

- (4) Wang, H.; et al. Integrated Circuits Based on Bilayer MoS2 Transistors. *Nano Lett.* **2012**, *12*, 4674–4680.

- (5) Wang H.; Hsu, A.; Palacios, T. Graphene Electronics for RF Applications. *IEE Microwave Magazine* **2011**, *13*, 114–25.

- (6) Hsu, A.; et al. Large-Area 2-D Electronics: Materials, Technology, and Devices. *Proc. IEEE* **2013**, *101*, 1638–1652.

- (7) Yu, L.; et al. Graphene/MoS2 Hybrid Technology for Large-Scale Two-Dimensional Electronics. *Nano Lett.* **2014**, *14*, 3055–3063.

- (8) Yoon, Y.; Ganapathi, K.; Salahuddin, S. How Good Can Monolayer MoS2 Transistors Be? *Nano Lett.* **2011**, *11*, 3768–3773.

- (9) Reina, A.; et al. Transferring and Identification of Single- and Few-Layer Graphene on Arbitrary Substrates. *J. Phys. Chem. C* **2008**, *112*, 17741–17744.

- (10) Bae, S.; et al. Roll-to-roll production of 30-in. graphene films for transparent electrodes. *Nat. Nanotechnol.* **2010**, *5*, 574–578.

- (11) Georgiou, T.; et al. Vertical field-effect transistor based on graphene-WS2 heterostructures for flexible and transparent electronics. *Nat. Nanotechnol.* **2012**, *8*, 100–103.

- (12) Tian, H.; et al. Graphene-on-Paper Sound Source Devices. ACS Nano 2011, 5, 4878–4885.

- (13) Tosun, M.; et al. High-Gain Inverters Based on WSe2 Complementary Field-Effect Transistors. ACS Nano 2014, 8, 4948–4953.

(14) Das, S.; Roelofs, A. Electrostatically doped WSe2 CMOS inverter. *Device Research Conference (DRC)*, 2014 72nd Annual; Santa Barbara, CA, June 22–25, 2014; IEEE, 2014; pp 185–186.

- (15) Rabaey, J. M.; Chandrakasan, A.; Nikolic, B. Digital integrated circuits a design perspective, 2nd ed.; Prentice Hall: New York, 2003.

- (16) Yu, W. J.; et al. *Vertically stacked multi-heteros*tructures of layered materials for logic transistors and complementary inverters. *Nat. Mater.* **2013**, *12*, 246–252.

- (17) Liu, H.; Neal, A. T.; Zhu, Z.; Tomanek, D.; Ye, P. D. Phosphorene: A New 2D Material with High Carrier Mobility. *ACS Nano* **2014**, *8*, 4033–4041.

- (18) Lui, C. H.; et al. Trion-Induced Negative Photoconductivity in Monolayer  $MoS_2$ . *Phys. Rev. Lett.* **2014**, *113*, 166801.

- (19) Nosho, Y.; Ohno, Y.; Kishimoto, S.; Mizutani, T. The effects of chemical doping with F4TCNQ in carbon nanotube field-effect transistors studied by the transmission-line-model technique. *Nanotechnology* **2007**, *18*, 415202.

- (20) Nourbakhsh, A.; et al. Tuning the Fermi Level of SiO2-Supported Single-Layer Graphene by Thermal Annealing. *J. Phys. Chem. C* **2010**, *114*, 6894–6900.

- (21) Song, S. M.; Cho, B. J. Investigation of interaction between graphene and dielectrics. *Nanotechnology* **2010**, *21*, 335706.

- (22) Yan, R.; et al. Thermal Conductivity of Monolayer Molybdenum Disulfide Obtained from Temperature-Dependent Raman Spectroscopy. *ACS Nano* **2014**, *8*, 986–993.

- (23) Gao, W.; Kahn, A. Controlled p-doping of zinc phthalocyanine by coevaporation with tetrafluorotetracyanoquinodimethane: A direct and inverse photoemission study. *Appl. Phys. Lett.* **2001**, *79*, 4040–4042.

- (24) Fang, H.; et al. High-Performance Single Layered WSe2 p-FETs with Chemically Doped Contacts. *Nano Lett.* **2012**, *12*, 3788–3792.

- (25) Ostroverkhova, O. Handbook of Organic Materials for Optical and (Opto)Electronic Devices: Properties and Applications; Elsevier: New York, 2013.

- (26) Huang, J.-K.; et al. Large-Area Synthesis of Highly Crystalline WSe2Monolayers and Device Applications. *ACS Nano* **2014**, *8*, 923–930.

- (27) Hunt, B.; et al. Massive Dirac Fermions and Hofstadter Butterfly in a van der Waals Heterostructure. *Science* **2013**, *340*, 1427–1430.

- (28) Soler, J. M.; et al. The SIESTA method for ab initio order-N materials simulation. *J. Phys.: Condens. Matter* **2002**, *14*, 2745.

- (29) Perdew, J. P.; Burke, K.; Ernzerhof, M. Generalized Gradient Approximation Made Simple. *Phys. Rev. Lett.* **1996**, *77*, 3865–3868.

- (30) Dion, M.; Rydberg, H.; Schröder, E.; Langreth, D. C.; Lundqvist, B. I. Van der Waals Density Functional for General Geometries. *Phys. Rev. Lett.* **2004**, *92*, 246401.

- (31) Troullier, N.; Martins, J. L. Efficient pseudopotentials for planewave calculations. *Phys. Rev. B: Condens. Matter Mater. Phys.* **1991**, 43, 1993–2006.

- (32) Monkhorst, H. J.; Pack, J. D. Special points for Brillouin-zone integrations. *Phys. Rev. B* **1976**, *13*, 5188–5192.