## 15-nm Channel Length MoS<sub>2</sub> FETs with Single- and Double-Gate structures

A.Nourbakhsh<sup>1,2</sup>, A. Zubair<sup>1</sup>, S. Huang<sup>1</sup>, X. Ling<sup>1</sup>, M.S. Dresselhaus<sup>1</sup>, J. Kong<sup>1</sup>, S. De Gendt<sup>2,3</sup> and T. Palacios<sup>1</sup> Massachusetts Institute of Technology, Cambridge MA 02139, USA, <sup>2</sup>imec, Kapeldreef 75, B-3001 Leuven, Belgium <sup>3</sup>KULeuven, Celestijnenlaan 200, B-3001 Leuven, Belgium; Email: anour@mit.edu

**Abstract**: We demonstrate single- and double-gated (SG & DG) field effect transistors (FETs) with a record source-drain length ( $L_{\rm S/D}$ ) of 15 nm built on monolayer ( $t_{ch}\sim 0.7$  nm) and 4-layer ( $t_{ch}\sim 3$  nm) MoS<sub>2</sub> channels using monolayer graphene as the Source/Drain contacts. The best devices, corresponding to DG 4-layer MoS<sub>2</sub>-FETs with  $L_{\rm S/D}=15$  nm, had an  $I_{\rm on}/I_{\rm off}$  in excess of  $10^6$  and a minimum subthreshold swing (SS<sub>min</sub>.) of 90 mV/dec. at  $V_{\rm DS}=0.5$  V. At  $L_{\rm S/D}=1$  µm and  $V_{\rm DS}=0.5$  V, SS<sub>min</sub>=66 mV/dec., which is the best SS reported in MoS<sub>2</sub> FETs, indicating the high quality of the interface and the enhanced channel electrostatics.

**Introduction:** Atomically thin-films lavered semiconductors such as MoS<sub>2</sub> have great potential in device applications because of their ultra-thin body nature, large bandgap, thermal stability and compatibility with CMOS processes [1, 2].  $MoS_2$  FETs have an extremely low  $I_{off}$ , making them promising for low power applications [2]. Also, FETs built on a few layers of MoS<sub>2</sub> are effectively ultra-thin body FETs (UTB-FETs), which are immune to short channel effects (SCE) [3]. Also, the smaller dielectric constant ( $\varepsilon_s$ ) of  $MoS_2$  compared with Si (6.8~7.1 vs 11.9) can further suppress the SCE [4]. The minimum channel length required to maintain long channel behavior is on the order of 4 times the characteristic length  $(L_{\min}=4\lambda)$ , where  $\lambda=\sqrt{(1/N)}.\sqrt{(\varepsilon_{\rm s}.t_{\rm s}.t_{\rm ox}/\varepsilon_{\rm ox})}$ for a planar FET,  $\varepsilon_s/t_s$  and  $\varepsilon_{ox}/t_{ox}$  are the dielectric constant/thickness of the channel and oxide, respectively and N=1 for SG and N=2 for DG FETs. However, this formula assumes that the S/D electric field lines are mostly confined in the channel to minimize the impact from the surrounding environment. For this, the S/D electrodes that are in immediate contact with the channel need to be as thin as the channel. To meet this requirement, monolayer graphene ( $t\sim0.4$  nm), was used as the S/D in this work.

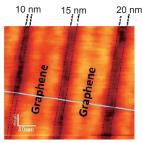

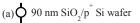

**Device Fabrication:** The key steps for fabricating SG & DG MoS<sub>2</sub> FETs with graphene S/D contacts, as well as a schematic of the devices are shown in Fig. 1. Either CVD grown monolayer or a mechanically exfoliated 4-layer MoS<sub>2</sub> was transferred onto a [p<sup>+</sup> Si/native SiO<sub>2</sub>] substrate coated with 10 nm of HfO<sub>2</sub> (EOT=3.3 nm) as the back gate (BG). Subsequently, monolayer graphene was transferred onto the MoS<sub>2</sub> layer. High resolution PMMA trenches ranging from 60 to 15 nm were patterned on the MoS<sub>2</sub>/graphene stack by the cold development (-15 °C) of 25 nm thick PMMA films followed by selective etching of the graphene with a mild indirect pulsed O<sub>2</sub> plasma, opening narrow slits down to 15 nm in the conductive graphene layer, defining the S/D channel. This process, which is suitable for UTB-FETs, is comparable to the metal dry-etching process used to fabricate S/D and gate electrodes in advanced CMOS fabrication [5]. Details on the pulsed plasma etch process are reported in [6]. After dry removal of the PMMA by a forming gas anneal, 1 nm air-oxidized Al<sub>2</sub>O<sub>3</sub> was deposited as a seed layer for subsequent ALD deposition of 10 nm HfO2 and 50 nm of Ni gate electrode onto the channel to build the top gate (TG). Fig. 2 shows an AFM image of the graphene slits ranging from 10 to 20 nm before TG deposition.

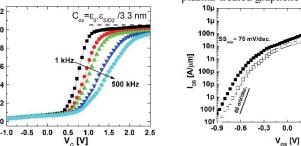

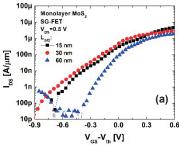

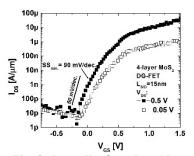

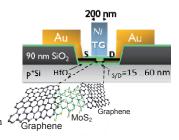

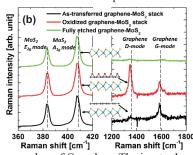

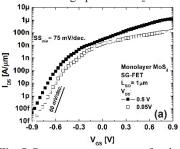

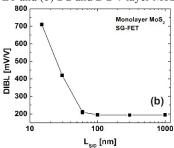

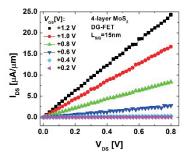

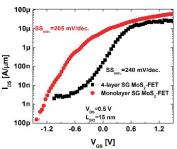

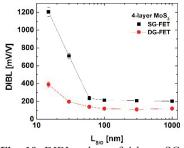

**Results and discussion:** The sheet resistance characteristics of monolayer graphene after different numbers of O2 plasma pulses are depicted in Fig. 3(a). After a sufficient number of pulses, graphene is eventually etched away, leaving a well-defined graphene slit, which defines the atomically-thin S/D contact. The etching of the graphene was well controlled with minimum impact on the underlying MoS<sub>2</sub> layer, as confirmed by Raman spectroscopy (Fig. 3(b)). The capacitance-voltage (C-V) characteristics depicted in Fig. 4 show that  $MoS_2$  is a natural n-type semiconductor. Therefore, MoS<sub>2</sub>-FETs operate in the accumulation-mode. Fig. 5 compares the transfer characteristics of long channel ( $L_{S/D}=1$ μm) monolayer and 4-layer MoS<sub>2</sub> FETs. The monolayer FET had an  $I_{\text{on}}/I_{\text{off}}$  in excess of 10<sup>7</sup> and SS<sub>min.</sub>=75 mV/dec, while the SG 4-layer FET had a smaller  $I_{\rm on}/I_{\rm off}$  and a larger SS<sub>min</sub> (105) mV/dec) (Fig. 5(b)). This difference is attributed to the better channel electrostatic control in monolayer vs multilayer FETs. However, the performance can be significantly enhanced by adding a TG electrode, which improved the SS<sub>min.</sub> to 66 mV/dec and  $I_{\rm on}/I_{\rm off}$  to ~10<sup>7</sup> (Fig. 5(b)). Long and short channel DG monolayer MoS<sub>2</sub> FETs were not fabricated in this study as seeding ALD high-k dielectrics on monolayer MoS<sub>2</sub> drastically shifts the  $V_{th}$  and therefore  $I_{off}$ , while multilayer FETs are significantly less sensitive to the high-k deposition process. The transfer characteristics of 15, 30 and 60 nm SG monolayer MoS<sub>2</sub> FETs are compared in Fig. 6(a). The occurrence of SCE in the 15 and 30 nm FETs caused their  $I_{\rm off}$  to drastically increase, which is in agreement with drain-induced barrier lowering (DIBL) (Fig. 6(b)) showing an upturn at  $L_{S/D}$ =30 nm. However, as expected, the SCE was stronger in the SG 4-layer FET, resulting in larger SS and  $I_{\text{off}}$  (see Figs 7). Nevertheless, the subthreshold characteristics of 4-layer MoS<sub>2</sub> could be significantly enhanced by integrating a TG, taking into account that favorably 4-layer MoS<sub>2</sub> has better potential for digital application due to its higher mobility resulting from its higher density of states and lower interface effects compared to monolayer  $MoS_2$  [7]. Figs 8 & 9 show the device characteristics of a 4-layer MoS<sub>2</sub>-FET in the DG configuration. The MoS<sub>2</sub> FET had  $I_{\text{on}}/I_{\text{off}} = \sim 10^6$ ,  $I_{\text{on}} = \sim 50 \,\mu\text{A/}\mu\text{m}$  and SS<sub>min</sub>=90 mV/dec. at  $V_{\rm DS}$ =0.5 V. For this device,  $L_{\rm min.}$ (=4 $\lambda$ ) in its SG configuration was ~17 nm (> $L_{S/D}$ =15 nm), while in DG  $L_{\text{min.}}=\sim 11$  nm, which is in agreement with the downshift of the upturn point in DIBL (Fig. 10) to  $L_{S/D}$ =15 nm with a relatively low maximum. The DIBL values indicate that the SCE was suppressed.

**Conclusions:** We have demonstrated MoS<sub>2</sub> UTB-FETs scaled-down to  $L_{\rm S/D}$ =15 nm with monolayer graphene contacts. The best  $L_{\rm S/D}$ =15 nm performance was achieved in a DG 4-layer MoS<sub>2</sub>-FET with  $I_{\rm on}/I_{\rm off}$ =10<sup>6</sup> and SS<sub>min</sub>=90 mV/dec. at  $V_{\rm DS}$ =0.5 V. This transistor has the shortest operating channel length of any MoS<sub>2</sub> transistor to date. The device performance indicates further scaling to sub  $L_{\rm S/D}$ =10 nm is possible.

**Acknowledgments:** A.N. acknowledges FWO-Flanders for a research fellowship. This work has been partially funded by the ONR PECASE program, monitored by Dr. Paul Maki and the NSF/DMR under award numbers 0845358 & 1004147.

## **References:**

[1]B. Radisavljevic, et al., Nat. Nano. Vol. 6, no. 3, p 147, 2011

[2]W. Cao et al., IEDM 2014

[3] Y. Yoon et al., Nano Lett., p. 3768,

[4]W. Zhu et al., Nat. Comm 5, 3087, 2014 [5] L. Yu, et al., Nano Lett. 14, 3055, 2014 [6]A. Nourbakhsh et al., Nanotechnology, 21, 435203, 2010

[7]J. Kang et al., APL., 104, 09319=06, 2014

atmosphere at 360 °C.

Capacitance [μF/cm<sup>2</sup>]

0.8

0.6

0.4

0.2

Fig. 2. AFM images showing 10, 15 and 20 nm graphene slits, after the PMMA was removed in an Ar/H<sub>2</sub>

Fig. 4. Accumulation C-V for MoS<sub>2</sub> MOS capacitor with EOT=3.3 nm.

Fig. 6. (a) Transfer characteristics of 15, 30 and 60 nm SG monolayer  $MoS_2$ FETs with graphene S/D contacts. (b) DIBL of monolayer SG MoS<sub>2</sub> FETs at various  $L_{S/D}$  values. There is an upturn at  $L_{S/D} \sim 30$  nm and a DIBL saturation of  $\sim 200 \text{ mV/V}.$

**Fig. 8.**  $I_{\rm DS}$  vs  $V_{\rm GS}$  for a  $L_{\rm S/D}$ =15 nm 4-layer DG MoS<sub>2</sub> FET with record performance values including  $SS_{min.}$ =90 mV/dec. and  $I_{off}$  $<10 \text{ pA/}\mu\text{m}$ .

(b) (i) SiO<sub>2</sub> wet etch by HF, (ii) ALD HfO<sub>2</sub>, (iii) anneal

Transfer of Graphene/MoS<sub>2</sub> stack

Selective etching of graphene to define S/D channel (d)

O S/D contacts and measurement pad metallization (e

Top gate ALD HfO<sub>2</sub> followed by top gate metallization

Fig. 1. Fabrication process flow and device schematic cross-section of the short channel SG & DG-MoS<sub>2</sub> FETs with graphene S/D contacts. Step (b) includes ALD-HfO<sub>2</sub> at 200 °C, followed by annealing in a forming gas at 400 °C. The SG-FETs fabrication process excludes step (f).

Fig. 3. (a) Graphene (oxide) sheet resistance vs number of O<sub>2</sub> pulses. The insets show schematics of a plasma pulse (power ramp from 0 to 100 W in 3 s) and the plasma setup with a device placed upside-down for indirect plasma exposure. (b) The evolution of Raman spectra of O<sub>2</sub> plasma-treated graphene-MoS<sub>2</sub> stack.

10µ

100n

4-layer MoS

10n 1n 100p 10p 1p (b) 0.0 0.2 0.4 0.6 0.8 **V**<sub>GS</sub> [V]

Fig. 5. Room temperature transfer characteristics of a 1 µm long channel (a) SG monolayer MoS<sub>2</sub> FET and (b) SG and DG 4-layer MoS<sub>2</sub> FETs.

Fig. 9.  $I_{\rm DS}$  vs  $V_{\rm DS}$  for the MoS<sub>2</sub>-FET in Fig. 8 for various  $V_{\rm GS}$  values.

**Fig. 7.** Transfer characteristics of  $L_{S/D}$ =15 nm SG monolayer and 4-layer MoS<sub>2</sub>-FETs. The stronger SCE in the 4-layer FET caused a larger  $I_{\rm off}$  and increased SS<sub>min</sub> compared with their respective values in the monolayer FETs.

Fig. 10. DIBL values of 4-layer SG & DG FETs. The DG has a downshifted upward turning point compared with the SG FET and its maximum shows a three-fold decrease.